NxN MIMO基站与外部时序参考同步

同步的一个重要结果就是“保持”的概念。如果时序参考丢失(例如,建筑物在每天的某一时间段挡住GPS卫星信号),参考时钟必须保持与存在时序参考情况下一样的状态。ANSI/T1.101-19873等标准将保持要求划分为多种层次,每种层次均规定了特定时间内允许的不同最大偏移。Stratum 3E是Bellcore GR-1244-CORE4所定义的一个附加层次,它要求时钟源在24小时内的偏移量不得超过亿分之一。

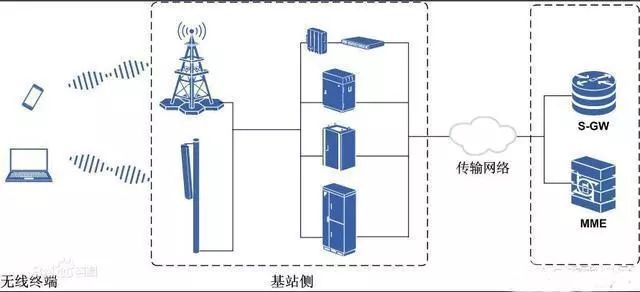

正如下面的N×N MIMO系统部分所述,如果一个基站在多输入多输出架构中使用两个或更多收发器,该基站必须使所有收发器与同一时序参考同步。为了降低器件数量及成本,参考时钟应能够提供多个完全相同的输出,每个输出都能驱动不同的收发器模块。

案例研究:提供外部时钟

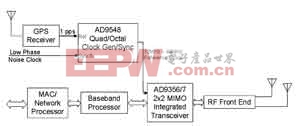

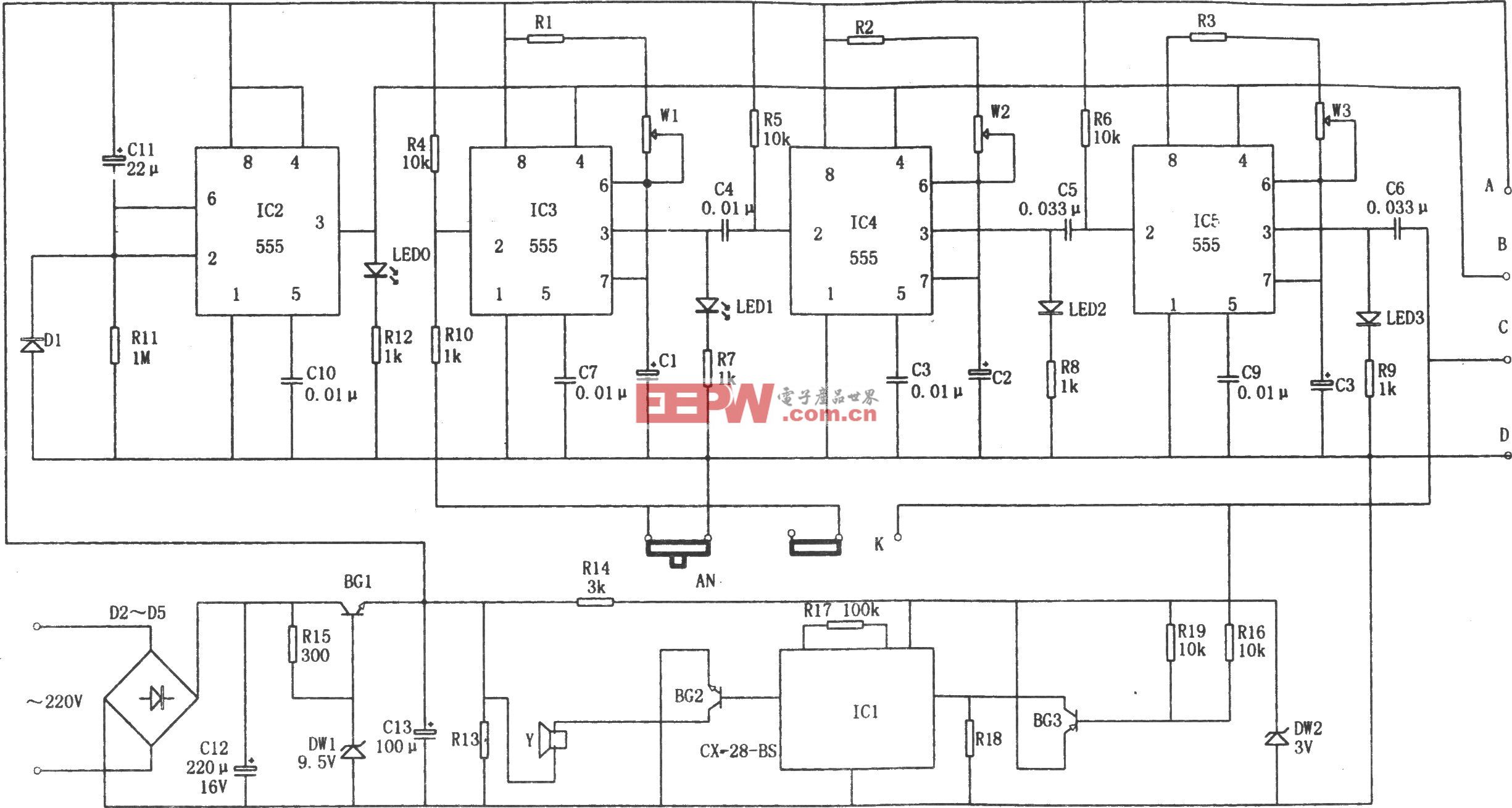

本案例研究使用AD9356/7 2×2 MIMO集成收发器作为基站系统的组成部分。如前所述,AD9356/7要求32~48MHz的参考时钟频率。要将此时钟与时序参考同步,需使用具有出色相位噪声性能的灵活PLL,像ADI公司的4/8通道输入网络时钟发生器/同步器AD9548完全符合这一要求。时序参考输出连接到AD9548的一路参考输入,一个低相位噪声时钟连接到系统时钟输入。输出设置为AD9356/7所需的32~48MHz参考时钟。图2显示了一个GPS同步系统的框图。

图2 采用GPS参考的基站架构

一些网络时钟发生器可以支持极宽的输入频率范围,从而提供各种不同的时序参考和低相位噪声时钟。明智选择输入频率可以简化设计,降低成本,实现最佳的发射和接收性能,并达到保持性能要求。

AD9548利用数字锁相环(DPLL)将输出时钟锁定至时序参考,而不是模拟PLL。这种技术可使系统实现极佳的保持性能,只受系统时钟源的时序漂移限制。此外,决定AD9548输出时钟相位噪声性能的因素是系统时钟的相位噪声,而不是时序参考,因此该器件可以接受高噪声时序参考,而不会将此噪声传递至其输出。

实现最高参考时钟性能

网络时钟发生器支持宽范围的输入和输出频率,从而为系统架构师优化输出时钟性能提供了许多选择。

例如,25MHz及以下频率的高稳定性时钟源相对更丰富,而且比更高频率时钟源便宜。如果图2所示的系统时钟(sysclk)输入小于50MHz,则可利用AD9548中的倍频器使系统时钟加倍,由此增加的相位噪声极小。然后利用这一更高频率,系统时钟PLL可将时钟提高到约1GHz。

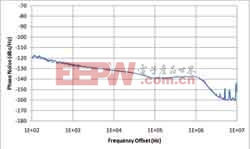

设计师还必须选择DPLL输出频率及由此产生的后置分频器比率。DPLL输出频率越高,则压摆率越快,一般有助于降低相位噪声,但也可能导致杂散折回频谱中。对于AD9356/7参考时钟,一个有效的折中选择是将DPLL输出频率设为240MHz,并将后置分频比设为6,得到40MHz的最终输出频率。图3显示了AD9548在这些设置下的相位噪声。

图3 ADI公司AD9548相位噪声与频率的关系

图4显示利用AD9548提供参考时钟,并以2500MHz进行传输时AD9356输出端的积分相位噪声。AD9548评估板可以利用其自有片内系统时钟XO(出厂配置)或外部时钟。图3和图4所示为AD9548使用一个12.8MHz恒温控制晶振(OCXO)作为其系统时钟输入的情况。此测试中,AD9548未与时序参考同步。

评论