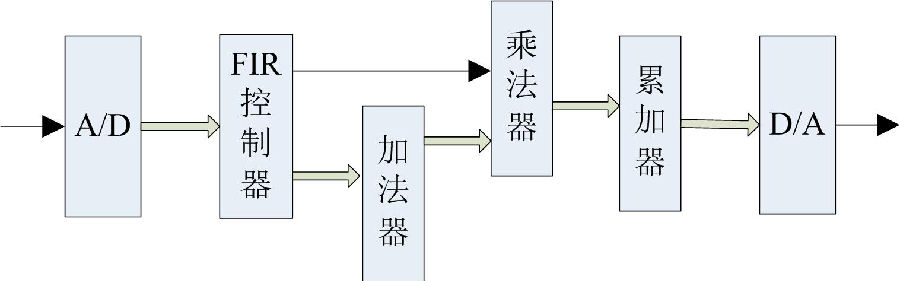

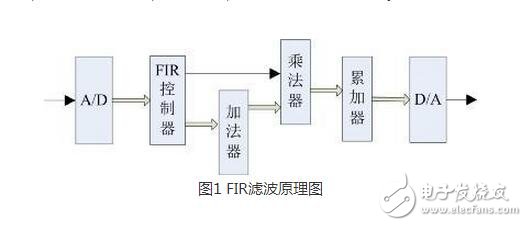

基于多软件平台协同工作的FIR滤波器设计

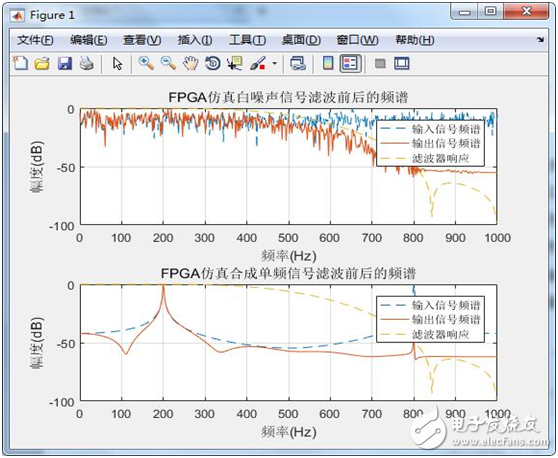

在搭建好的模型中加入两个正弦波合成的输入信号,运行仿真,通过Scope窗口观察滤波器时域仿真波形如图5所示。本文引用地址:https://www.eepw.com.cn/article/186603.htm

从仿真的结果看,FIR滤波器输入信号上面叠加的带外信号得到有效滤除,效果为理想。

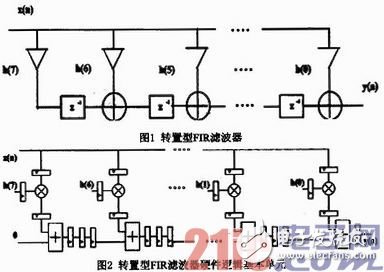

但是由于EDA工具软件(诸如QuartusⅡ和ModelSim)不能直接处理MATLab的.mdl文件,这就需要一个转换过.mdl)转化成通用的硬件描述语言——VHDL文件。转化后获得的HDL文件是基于RTL级的,即可综合的VHDL描述。然后对VHDL的RTL代码和仿真文件进行综合、编译适配及仿真。

2.3 后端模拟部分

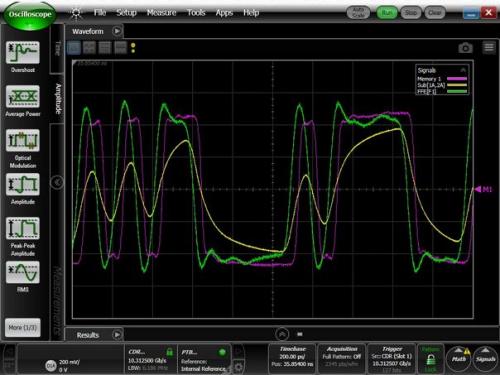

信号经过FIR数字滤波以后,生成的数字信号经过ispPAC20内部D/A转换器,将数字信号转换成模拟信号,然后通过ispPAC20内部器件进行最后的模拟滤波,滤除信号中的叠加的某些高频分量,经过实际验证,得到的信号能够满足设计要求。

2.4 系统整体功能的实现

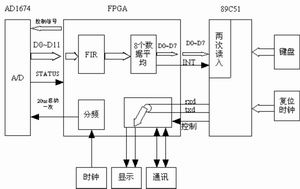

将原始信号经过ispPAC20的IN1口输入,经过内部程序的缓冲以及预滤波作用之后,将信号输入到比较器ep1的比较端口,然后与8位逐次逼近寄存器(SAR)输出的数字量经过内部D/A转换器输出的信号进行比较,从而完成从模拟信号到数字信号的转换过程。经过FPGA对转换后的数字信号的滤波处理之后,从FPGA的管脚输出,再通过后端ispPAC20的D/A转换器以及内部的运放以及输出滤波等程序,将信号从ispPAC 20输出,从而完成系统的整个功能。

3 结束语

本系统改变了传统的只用硬件电路设计的方法,系统中前端模拟部分和后端模拟部分均采用可编程模拟器件(ispPAC)实现,使用高度集成化芯片,系统的可靠性与稳定性有所提高,而且利用FPGA可以根据自己的要求重复配置各种精度和特性的FIR滤波器,使设计更为灵活,但由于利用ispPAC20和FPGA构建的A/D转换器在转换精度和速率上有一定的限制,所以此系统在实际工程应用中还存在一定的局限性。

评论