加强ESD保护的技巧

LIC和LPORT

很多ESD器件数据手册中经常提到让器件尽可能靠近ESD输入点。这样LPORT/LIC比就会尽可能得低(即LIC>>LPORT)。LPORT的电感未必会影响整体的ESD性能,但LIC的电感则肯定会影响ESD性能。

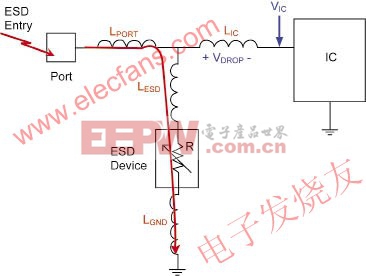

LIC的非线性会通过大幅削减IC电压来充当ESD脉冲的初始峰值电流的缓冲器。随着电感的降低(即ESD器件越来越靠近IC),电压降也会不断减小,直到无法获得任何优势时为止。所以,将LPORT/LIC比降至最低以便利用PCB迹线的寄生特性对设计者最有利。我们所说的电压降如图4所示。

图4

利用LIC和LPORT是提升整体ESD性能的直接方法。然而,无论上述比值有多小,仍然有设计会过早地出现故障。换句话说,LIC未能为峰值ESD电流提供充足的缓冲。

有时候,采用先前的技术不足以为给定电路板设计提供最大限度的ESD保护。原因在于流经“片上”ESD结构的电流过多,并且在I/O短接至GND或VCC时被损坏。

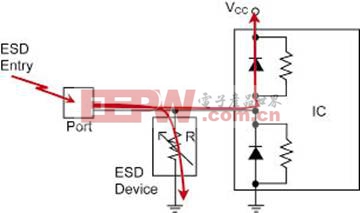

图5有助于将它弄清楚,表明ESD器件和受保护的IC实际上共同承担了来自于ESD脉冲的电流负载。该数值(负迹线电感)对应于正ESD脉冲,其中保护器件吸收了大多数电流,但是它本质上是一个带有IC的电阻分压器。

图5

如图5所示,IC上的轨对轨二极管负责将剩余的或“允通”电流导入VCC(它一般会通过旁路电容器回到GND)。很难确定什么样的等效电阻适于为IC实现ESD保护,但是无疑比板上ESD器件高得多。

电机保护器相关文章:电机保护器原理 红外热像仪相关文章:红外热像仪原理

评论