一种高速连续时间Sigma-Delta ADC设计

4 实验结果

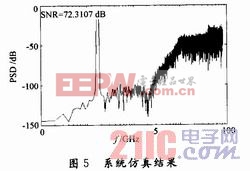

通过Candence提取系统版图后仿真电路,在不同工艺角下对使用HSpice对系统进行后仿真,得到系统SNDR如图5所示(TT工艺角下),最大SNDR可达63.6176 dB,输入差分信号幅度为O.55 V。

针对CT Sigma-Delta ADC各种结构对时钟抖动的忍受能力这一问题,将本文结构与其他论文进行对比,结果如表1所示。可见,该设计对时钟抖动的忍受能力是很强的。

5 结语

采用TSMC O.18μm CMOS工艺,在1.8 V电源电压下设计了一款连续时间Sigma-Delta ADC调制器,完成了电路设计和版图绘制。经后仿真验证此Sig-ma-Delta ADC调制器带宽达到5 MHz,信噪比SNDR可达63.6 dB。芯片在硅片上所占面积为1.5 mm×1.5 mm,而其调制器本身所占面积只有O.9 mm×0.9 mm,功耗仅为32 mW。与同类设计进行比较,该设计对时钟抖动的忍受能力是很强的。

本文引用地址:https://www.eepw.com.cn/article/180055.htm

评论