一种高速连续时间Sigma-Delta ADC设计

1.2 时钟抖动

时钟抖动(clock jitter)对连续时间Sigma-DeltaADC的影响要比对离散时间Sigma-Delta ADC的影响大的多。时钟抖动对连续时间Sigm-aDelta ADC的影响主要体现在采样电路和DAC上。由于采样电路在滤波器之后,它产生的噪声被环路滤波三阶整形,而DAC产生的噪声有一部分直接加在输入信号上而未被整形,所以可以认为时钟抖动对信噪比的影响集中于DAC产生的噪声上。对于采用的非回零(NRZ)反馈DAC,可以把抖动噪声表示为式(4):

△TDAC[n]为采样时钟的抖动误差。将抖动噪声的方差表示为式(5):

其中dy=y[n]-y[n-1]。利用式(4)和(5),根据文献对系统受时钟抖动的影响进行建模仿真,可以得到,调制器在时钟抖动大约为30 ps时,SNR仍可保持在64 dB以上。

2 电路结构设计

在系统建模达到要求之后,采用图1(b)中的实际电路来实现系统的建模。电路包括三阶一位环路RC积分滤波结构、四输入一位量化器以及一位电压型NRZ DAC,采用RC积分滤波是因为这种滤波形式有更好的线性度和输出电压摆幅,可以实现更高的信噪比,同时为反馈DAC提供更好的虚拟地端。系统中采用由时钟控制的DFF实现所需的半个周期的延时。

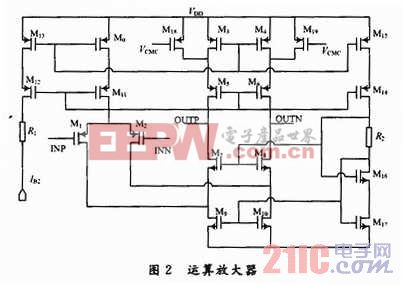

2.1 运算放大器

在环路设计中,运算放大器的设计是关键。对运算放大器进行建模,仿真得到在满足系统要达到的指标要求的情况下,运算放大器的DC Gain至少到达55 dB,增益带宽积GBW要达到2~3倍的采样频率,约为650~900 MHz。在设计中,选择电阻自偏置的折叠共源共栅放大器,如图2所示。

在设计中,VCMC为运放共模反馈电压,为电路提供稳定的共模电平。两个含有电阻支路为整体电路提供偏置,由IB2端输入基准电流。在CMOS标准工艺中,电阻的绝对值的大小变化很大。仿真显示,该设计中所采用的偏置电阻的值在8.4~15.6 kΩ之间变化时,偏置电路仍可为整体电路提供适当的偏压,运算放大器各指标所受的影响较小,仍可满足系统的要求。

评论