新型磁耦合隔离电路设计

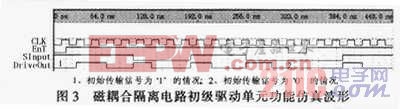

3.1.3 初级驱动单元的功能仿真

使用QuartusII 9.0对磁耦合隔离电路初级驱动单元进行功能仿真,得到功能仿真曲线如图3所示。本文引用地址:https://www.eepw.com.cn/article/179136.htm

从上图看出,在1的位置后,虽然没有输入信号(SInput)的变化,输出驱动波形中也产生了一个驱动脉冲,这就是为了保证在输入信号初始值为高电平时保持输入和输出的一致,由电路自动加入的;在位置2,复位后次级接收电路初始态已经为低电平,输入信号的初始值也为低电平,隔离输入输出一致,故不需要自动加入驱动脉冲。

3.2 次级接收模块的实现

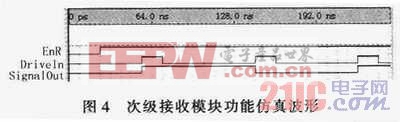

Receive构成磁耦合隔离电路的次缀接收模块,该模块完成的功能为:在复位信号到来后,接收电路复位输出为‘0’,而后每接收到一个脉冲,输出反转一次。由于复位后接收模块的初始态已与初级输入信号的初始值一致,初级输入信号每发生一次跳变,初级驱动电路输出一个脉冲,因此在任何时刻,次级接收电路的输出都与初级输入信号一致。从而实现低频或直流信号的磁耦合隔离传输。该模块实际上就是一个带复位功能的一位计数器,关于它的VHDL实现在参考文献中有现成的例子,此处不再赘述。

InputS模块的功能仿真波形如图4所示。

3.3 模块工作频率的说明

一般来说,对于上升沿持续时间在50ns左右脉冲变压器,传输信号跳变沿驱动脉冲的宽度至少应大于此时间,在本设计中,选用60 ns的脉冲作为传输信号跳变沿驱动脉冲的宽度,为了使两个相邻的传输信号跳变沿驱动脉冲能够被接收模块准确识别,它们之间应至少间隔一个脉冲宽度的时间,这样算起来,传输信号的最短持续时间应为120ns,而对于直流信号上述模块也能准确传输(原理前面已经述及),因此该模块传输信号的频率范围是0~8 MHz。对于高于8 MHz的数字信号,模块将不能正确工作。

上述分析是在脉冲变压器上升沿为50ns的前提下给出的,如果上升沿时间再短些,模块的工作频率上限还可提高。

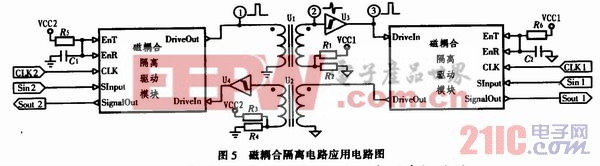

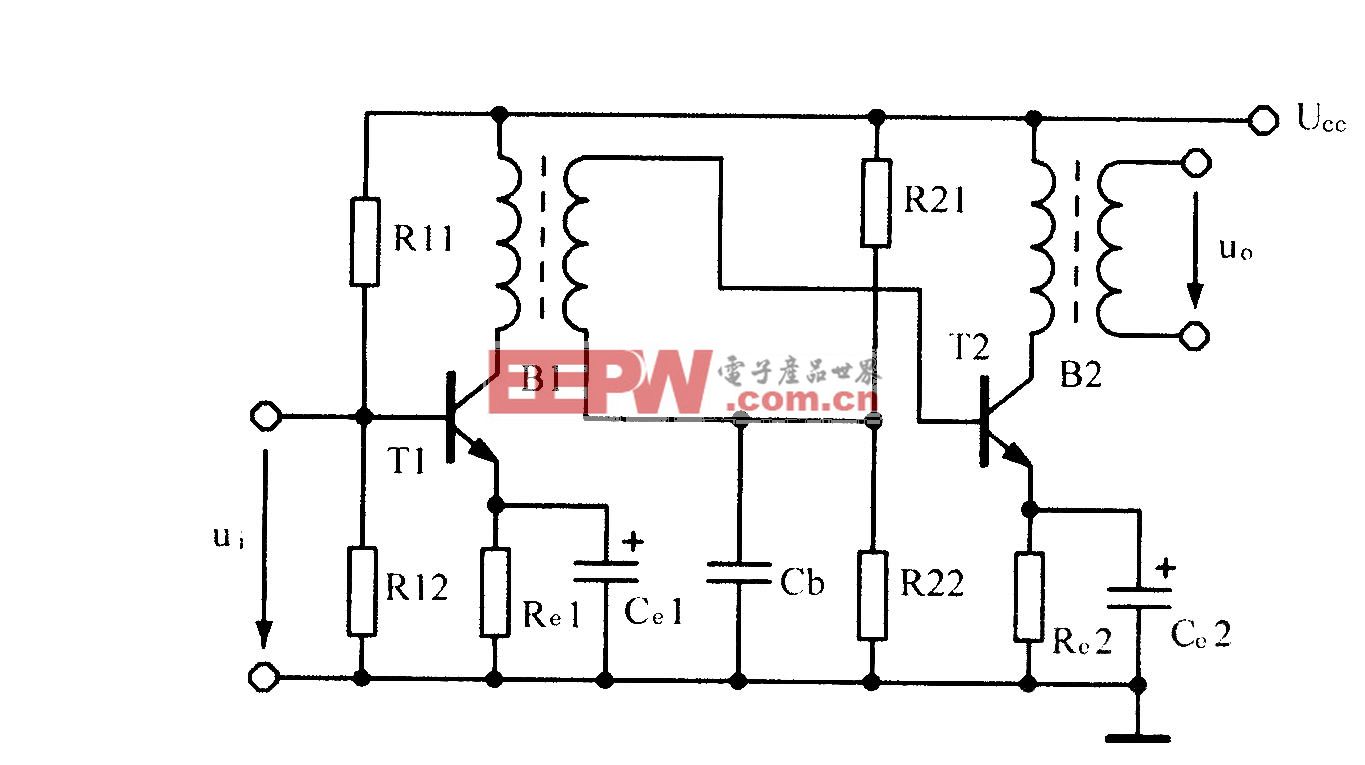

3.4 新受磁耦合隔离电路应用

新型磁耦合隔离模块的应用电路如图5所示,该电路用于完成信号Sin1到Sour2,Sin2到Sout1的磁耦合隔离传输。在电路中,U1、U2为脉冲变压器ITNA-0235-D103,上升沿持续时间50 ns;U3、U4为Schmitt触发器,用于将脉冲变压器输出的信号整形成脉冲信号,测试点①② ③的信号波形如图前面中所示。R5、C1和R6、C2分别组成两个磁耦合隔离驱动模块的上电复位电路,两个复位电路的时间常数应设计在10μs左右,以保证模块稳定复位;R1、R2和R3、R4分别组成两个电平移动电路,用于将脉冲变压器输出的交流信号移动到0~VCC的范围。在模块配置到CPLD时DriveOut引脚必须配置成ITL模式以增加电流驱动能力。电路在实际使用时,EnT与EnR可以改成由逻辑信号直接控制,这样就可以使驱动模块稳定时间可控,在由于受到干扰而使电路出现错误时,可以通过施加EnT与EnR信号使电路恢复正常工作。

对上述电路测试,得到如下测试结果:

1)电路能够准确传输直流信号;

2)对小于8 MHz的数字信号跳变沿的传输延迟小于50 ns,对于8 MHz以上的数字信号上述电路不能工作;

3)电路功耗,由于用于信号传输驱动的逻辑电路只占CPLD的很小部分(在应用电路中,CPLD选用EPM240TC100,使用16个逻辑单元,占总逻辑单元数的7%,其他单元用作别的用途),准确功耗很难测量,但是在传输直流信号时磁耦合隔离部分的功耗与光隔的功耗对比就足以说明问题。传输高电平时,光隔电路需要持续消耗10 mA的电流,以维持稳定输出高电平;而上述磁耦合隔离电路则只需要在最初的40 ns内消耗电流,其他时间磁耦合隔离部分消耗的电流为0,因此传输直流信号时,上述电路的功耗要远小于光隔电路。

4 结论

该设计的创新点在于:1)以窄脉冲表示传输信号的状态改变;2)以窄脉冲的磁耦合隔离传输代替输入信号的隔离传输,降低隔离电路的功耗;3)实现低频和直流信号的磁耦合隔离传输;4)驱动电路简单,接收和发送模块共需要16个逻辑单元就可实现上述功能;5)信号传输延迟很小。

存在的问题:1)传输信号的上限频率受限,只能传输0~8 MHz的方波信号;2)在电路上电到复位信号结束的一段时间(10μs以内),电路不能正确传输信号,必须保证在此时间段内传输信号状态稳定,否则后面的信号将全部错误。

总之,正是由于该设计具有电路简单、功耗小、能够实现磁耦合隔离传输低频信号,且信号传输延迟很小等特点,拓展了磁耦合隔离技术的应用领域。

评论