一种电子系统认证芯片的电源规划

摘要:为了对所开发的电子产品进行保护,采用ASIC的方法设计基于硬加密技术的电子系统认证芯片。在后端物理设计中,为了使最终的芯片实现面积优化且满足功耗、时序等要求,采用预设计的方法对芯片进行功耗预估与布线拥塞分析。根据分析结果提高了芯片利用率,并针对预设计中存在的电压降(IR Drop)违规进行了详细的电源规划,包括全局电源网络的连接、电源环和电源条的设计,最终满足了功耗要求,实现了时序收敛以及面积优化。

关键词:系统认证;电源规划;功耗分析;电压降

0 引言

为了防止所研发的电子产品被非法克隆,一种有效的方法是采用硬加密技术对电子产品进行保护。硬加密技术是指依赖特定的硬件实现系统保护,主机需要访问相应的硬件进行认证后才能正常工作,具有抗解密强度高,稳定性和兼容性好等优点。

本文所研究的电子系统认证芯片是基于硬加密技术采用专用集成电路(ASIC)设计的方法来实现的。由于ASIC上有特殊算法,PCB和一些硬件可能被复制,但是无法复制ASIC的加密数据,保密性更强。该芯片采用RSA加密算法,它是非对称密钥密码体制的代表,其安全性在于找到两个大素数p和q比较容易;但目前没有有效的方法从p和q的乘积N中分解出p和q。有专家建议,普通公司使用1 024位的密钥就可以保证资料的安全性,因此该系统认证芯片采用密钥为1 024位的RSA加密算法。

该电子系统认证芯片采用SMIC 0.18μm 6层金属工艺,在SoC Eneounter平台上进行物理设计。为了了解整个芯片的布线拥塞程度和功耗的大概情况,进行正式设计之前,对该芯片进行预设计;通过预设计的结果分析芯片的布线拥塞情况,并对布局布线后的功耗进行预估。在分析预设计的基础上,针对预设计中存在的问题对芯片进行详细的电源规划,为整个芯片设计出一个合理的供电网络,使最终的设计实现面积优化,并且满足功耗、时序等要求。

1 功耗预估

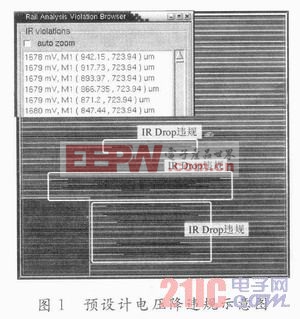

预设计采用75%的利用率,对该电子系统认证芯片进行了粗略的布图规划,仅设计了宽度为10 μm的电源环。为了使芯片功耗的分析结果更接近实际,对该芯片进行了布局、时钟树综合和详细布线等步骤。在时序收敛的前提下,进行功耗分析,工作电压VDD为1.8 V,得到芯片的总功耗为115.41 mW,包括开关功耗(Switehing Power)、内部功耗(Internal Power)和泄露功耗(Leakage Power)。但是芯片中存在IRDrop违规(即芯片中的电压降超过了5%VDD),如图1所示,左上角的对话框中列出了存在IR Drop违规的地方,具体位置在版图中的深色区域。一般情况下,5%的电压降会增大10%~15%的线延迟,会产生时序违规,使芯片处于不正常的工作状态,因此,需要在后续设计中进行详细的电源规划。

采用75%的利用率进行详细布线后发现,版图中的布线拥塞情况并不严重,Meta15和Meta16的布线资源均比较宽裕。一些研究表明,芯片成本与芯片面积的4次方成正比。为了降低成本,应尽可能减小芯片面积。经过反复尝试之后,确定芯片的利用率为80%,芯片内核(Core)面积约为2.474 mm2,总面积约为3.5 mm2,比预设计时减小了约0.12 mm2。

2 电源规划

在该电子系统认证芯片的预设计阶段,存在IRDrop的违规,因此必须通过电源规划来设计芯片的供电网络,以消除IR Drop违规。电源规划的总体步骤包括全局电源网络的连接、电源/地Pad规划、电源环的设计和电源条的设计。

评论