一种改进的基于扫描的电路设计

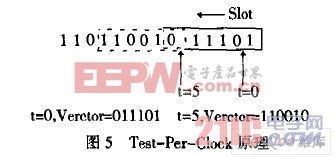

如图5所示,每个时钟周期。Slot会往左移动一位,即在Slot内产生一个新的测试向量,而Slot大小可以看成扫描链的大小。

不过,由于每个时钟都要作测试,所以每个时钟在测试后都会产生新的测试结果。传统的基于扫描的测试环境里,电路输出结果传送出来的同时也将新的测试传进扫描链里。

如果输出的向量只有一位就不会有这样的问题。

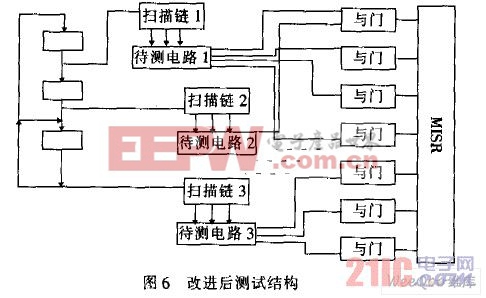

因为我们现在要产生一个新的测试向量所需要的时间只有一个时钟周期,所以时问刚刚好。但是一般而言,待测电路的输出向量都会超过一位。所以我们在观察电路输出结果这个步骤上就会有问题。为了解决这个问题,需要对传统的基于扫描的测试电路做些修改。在待测电路的输出部分,可以用MISR来取代原来的扫描链电路,也就是将输出送到MISR做特征分析,如图6所示。

但是由于电路越来越复杂,电路的主要输入与输出的个数就会很多,如果对这样的待测电路加测试电路,将会出现外加电路面积过大的问题。所以我们针对MISR的部分提出一个方法,使得因测试而增加得MISR可以尽量地缩小。

缩小MISR的大小最直接的想法是将主要输出经组合电路压缩变小,但是这样会使错误覆盖率降低,使测试向量变多,这些问题在文献中谈到了。造成错误覆盖率降低的原因是如果我们将有共同输入向量的两个主要输出通过组合电路合并的话。将可能会造成原本可以测试到的错误,在合并后就测试不到了,所以造成了错误覆盖率的降低。

为了避免这个情况的发生,我们在向量压缩的过程中。只有将没有共同输入向量的主要输出合并在一起,就不会有问题出现了。如图6所示,两个不同的待测电路的主要输出经过合并以后输出到MISR,这样用一个与门代替了一个寄存器以便减少面积,而错误覆盖率则因为两两合并的主要输出端都没有相同的主要输出资料,所以就没有错误覆盖率降低的问题存在,即原来可以被侦测到的错误,在经过主要输出端合并之后仍然可以被侦测到。

4 结论

经过改进后的基于扫描的测试架构,用向量压缩来减少测试时间,并且将TEST—Per-Scan的测试方式改成了TEST—Per-Clock的测试方式,加快了测试的速度。

评论