检测LDMOS漏端电压判断是否过流方案

而当栅极电压V(GATEDelayed)为高电平时,输出比较电压则变为V(Compare)=I1×R3=1.0 V。

过流比较器过流比较器采用常见的NPN 差分对管的输入方式,恒流源偏置。与传统恒流源偏置略有不同的是在偏置电路中增加了MOS 开关,当V(GATE)为高时(此时LDMOS 和该MOS 开关同时导通),电路图左侧恒流源工作,使总偏置电流变大,输出缓冲级的驱动电流增大,比较电路速度加快;在V(GATE)为低时,左侧的恒流源不工作,总偏置电流变小(此时LDMOS 不导通,过流比较器处于闲置状态),为节能模式。

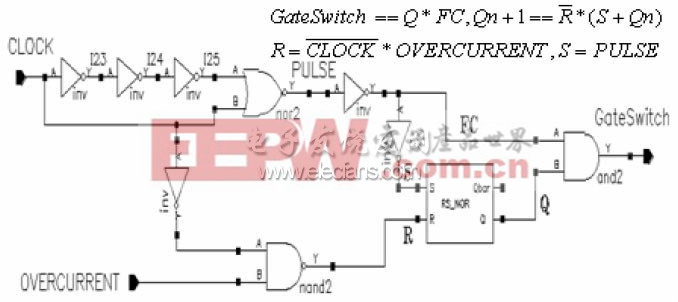

2.2 控制逻辑

控制逻辑模块如图4 所示,该模块直接控制LDMOS 的开关。PULSE 信号的上升沿对应是CLOCK 时钟的开始,PULSE 信号与时钟CLOCK 的关系如图9 所示。当发生过流时,OVERCURRENT信号为低,触发器R 端为高,Q 为低,GateSwitch 信号为低,关断LDMOS,从而实现过流保护功能。

图4 控制逻辑电路图

3 仿真结果

我们利用BCD 高压工艺,在cadence 环境下进行电路仿真验证。结果如下:

前沿消隐电路的仿真仿真条件:取电源电压为5.8 V,2 pF 的电容在10μA 的放电电流情况下,延迟时间为Tdelay=C*0.

5VDD/I =2p*2.9/10μ= 0.58μs,仿真结果如图5 所示。

图5 前沿消隐电路仿真

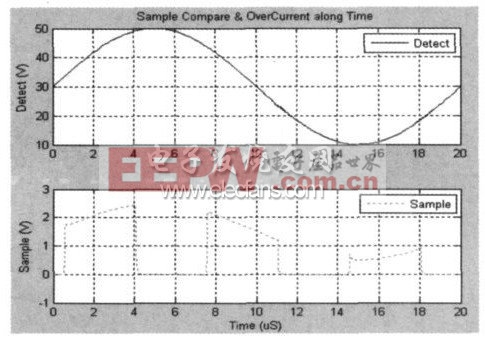

采样电路的仿真

设检测端电压一般在10~50 V 之间变化,我们设置V(Detect)=SIN(30,20,50 k);周期为20μS;又设在采样周期内,比较电压为1 V;依据LDMOS管导通特性,设输出漏电压高于某值(本例为20伏)为过流,则分压比设计为K = R4/ ( R3+R4)=5 k/(5 k+95 k)=1/20, 于是得到采样电压值为V(Sample)=V(Detect)*k =SIN(1.5,1,50 k),即最大值为2.5,最小值为0.5。同样地,我们在采样电路输出端加上一个电容以消除电压尖峰影响。该采样电路仿真结果如图6 所示。

图6 采样电路仿真

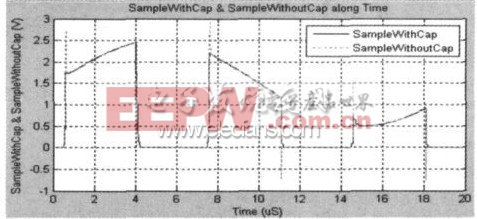

比较电压产生器的仿真

在比较电压产生器输出端应加上电容Ccompare,以消除由于开关管导通的瞬间在Ccompare端产生的尖峰电压,仿真结果如图7 所示,其中虚/ 实线分别为有无电容存在时的仿真结果。显然,电容Ccompare的存在极大地改善了输出波形。电容Ccompare大小的选择,应该权衡消峰效果、充电速度和芯片面积消耗间关系。

图7 添加电容Ccompare 前后的比较

本例中,取Ccompare为4 pF。

评论