基于CMOS多功能数字芯片的ESD保护电路设计

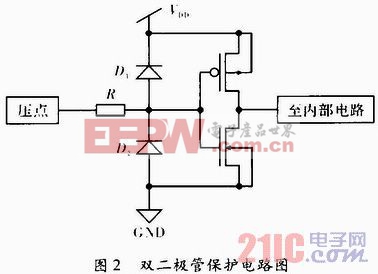

对CMOS集成电路连接到压点的输入端常采用双二极管保护电镀,图2所示为常见的ESD保护电路的结构:双二极管保护电路。二极管D1是和PMOS源、漏区同时形成的,是p+n-结构,二极管D2是和NMOS源、漏区同时形成的,是n+p-结构。当压点相对地出现负脉冲应力,则二极管D2导通,导通的二极管和电阻形成ESD电流的泄放通路。当压点相对地出现正脉冲应力,使二极管D2击穿,只要二极管D2击穿电压低于栅氧化层的击穿电压,就可以起到保护作用。类似的,当压点相对电源出现正脉冲或负脉冲应力,二极管D1起保护作用,提供静电荷的泄放通路。

这两个二极管把加到输入级MOS晶体管栅极的电压范围如式(1)所示。

-0.7VinVDD+0.7 (1)

假设二极管的正向导通电压是0.7 V。电阻的作用是限制流过二极管的电流。由于ESD应力电压都是短暂的脉冲信号,只要电流不是非常大,二极管不会被烧坏,可以持续起保护作用。图2中使用二极管作为I/O端的ESD保护电路,主要提供PD和NS模式下的电流泄放通路,但对于ND模式和PS模式,二极管处于反偏状态,反偏箝位电压过高,电流泄放能力较弱,导通电阻较高,使箝位能力不够,且产生的热量较大。

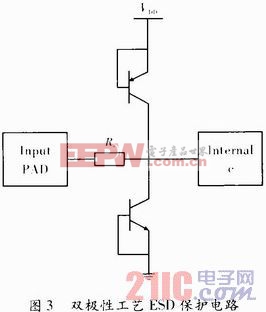

图3中电路主要用于双极工艺,采用一个基极接VDD地PNP三极管和一个基极接地的NPN三极管共同构成ESD保护电路。采用这种保护电路,相对于二极管,在ND和PS模式下,可以工作在Snapback状态,具有较强的电流泄放能力和较低的维持电压。

2 ESD保护电路

对深亚微米CMOS集成电路,栅氧化层的击穿电压很小,常规二极管的击穿电压较大,不能起到很好的保护作用。因此可以增加离子注入提高二极管的衬底浓度,形成p+n+和n+p+结构来降低二极管的击穿电压。

评论