数字电路设计中部分常见问题解析

摘要:借助一个双向计时器的设计电路,以举例的形式对数字电路设计中3个方面的常见问题进行了较为详尽地分析,并提出了一些见解,即针对控制设计方面在分析了其实质要求的基础上提出解决问题的关键是选取合适的输入控制信号和正确列出真值表或状态表,针对时序方面通过比较同步和异步的特点并指出可采用同步的“分频”和异步的“级联”完成设计,而针对引脚方面则解析了一般芯片中几个特殊引脚并准确阐述了其所蕴含的不容易被理解的概念。

关键词:问题解析;数字电路设计;控制;时序;引脚

21世纪是信息化时代,信息化时代又被称为数字时代,而其支撑基础就是数字电路,因此当前数字电路已被广泛应用于各个领域。数字电路是实现逻辑功能和进行各种数字运算的电路,数字电路设计主要包括:分析要求、确定方案、设计电路、组装调试等步骤。在各个设计步骤中,必然会遇到各式各样的问题,下面拟对数字电路设计的一些常见问题进行解析。

1 常见问题解析

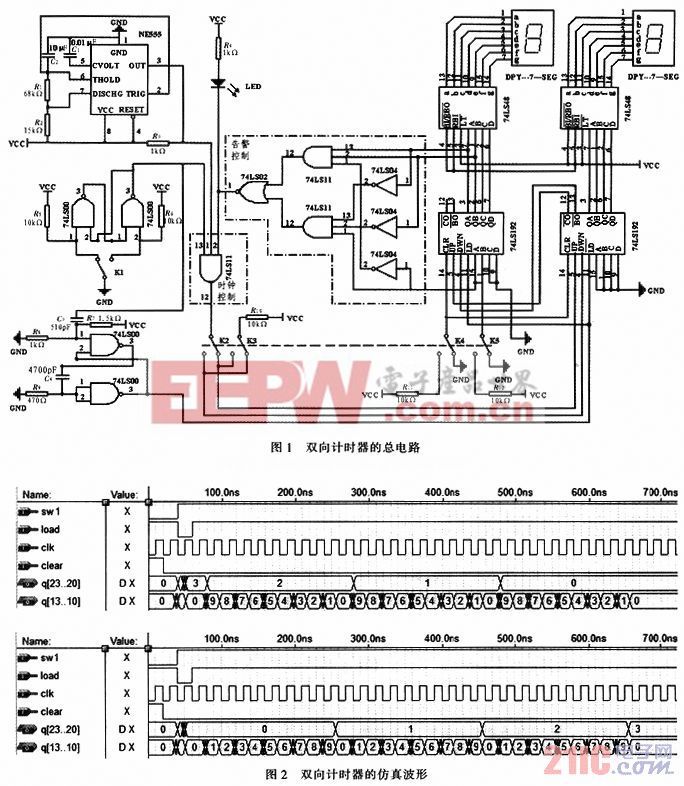

文中借助学生设计的双向(加减)计时器,如图1所示,来探讨电路设计中3个方面的常见问题。

图1所示的电路可实现0~30 s双向(即加减)计时,这是该电路的优点,因为目前常见的多为单向计时电路,图2所示为其仿真波形。该电路包括秒脉冲发生器、计数器、译码显示电路、各种控制电路等几个部分组成。具体为:由一个工作于多谐振荡模式的NE555产生1 Hz的时钟CP,经过时钟控制电路去激励两个异步时序的74LS192开始计数,计数输出给两个74LS48进行译码,最后由2个七段数码管完成计时显示,而控制部分主要包括:开关K1和RS锁存器完成计时开始和暂停、联动开关K2~K5和单稳态电路完成加减计数时钟切换和相应初值设定、LED和限值反馈控制电路完成告警、时钟CP控制等。

1.1 控制方面

在设计中,先对电路性能指标要求进行分析,然后确立设计方案(或原理框图),一般在此基础上选择合适的功能器件是很容易搭建出各主要功能模块的。但是,如何将各功能模块间正确的“联系”起来最终实现所有的电路功能,在实际设计中这往往是一个令人头痛的问题,相信许多设计者对此都有同感。

这里将此部分称为控制方面的设计问题,实质要求为:逻辑上需要用一些信号(称为控制信号)去决定某一个或一些信号(被控制信号)。对此的解决办法是:把此部分看作一个简单的逻辑电路(组合逻辑或时序逻辑)进行设计。因此,关键步骤是:选取合适的输入控制信号和正确列出真值表(对组合逻辑电路而言)或状态表(对时序逻辑电路而言)。

实际中,一般多属于组合逻辑情况,即此时刻输出状态由此时刻输入状态决定,体现“即时”控制的内涵。文中就探讨属组合逻辑的控制,且以前述电路中的告警控制和时钟控制为例。

1)告警控制

在图1电路中当正向加计时到30 s或者反向减计时到00 s时要求实现LED告警功能。

评论