基于可逆逻辑电路的脉冲分配器设计

2 可逆脉冲分配器的设计

在传统的不可逆时序电路中,使用的逻辑门是不可逆的。要设计可逆逻辑电路,就要使用可逆逻辑门进行构造。本文将传统的不可逆时序电路中的逻辑门替换成可逆逻辑门,不改变原有电路的设计原理,从而将不可逆逻辑电路转化为可逆逻辑电路。本文引用地址:https://www.eepw.com.cn/article/175771.htm

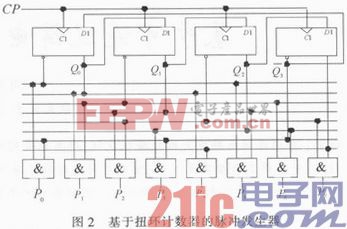

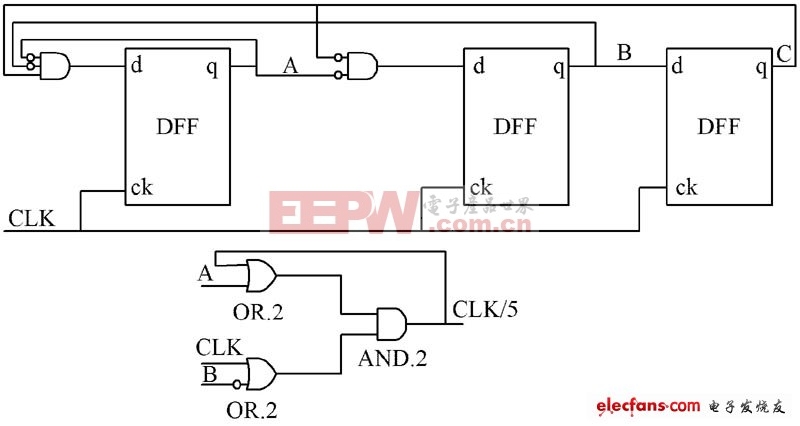

传统的可逆脉冲分配器主要是由计数器和相应的译码器组成,基于扭环计数器的脉冲分配器如图2所示。其中计数器又由触发器级联而成,所以要将其中的触发器和基本的与门转换成相应的可逆逻辑门,另外,由于可逆逻辑电路不能有扇入或者扇出,所以图2中的扇入扇出信号要用可逆逻辑门对信号进行复制。

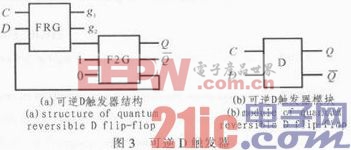

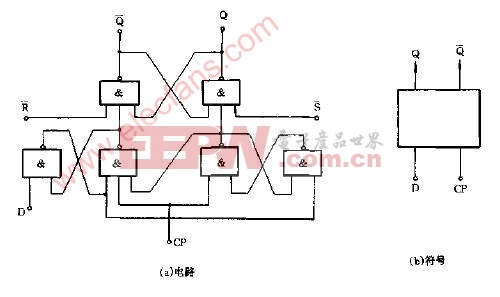

首先要将传统的D触发器转化可逆D触发器。考虑到量子代价和量子门数的影响,设计了由图1中的FRG门、F2G门构成的可逆D触发器,具体结构如图3所示。

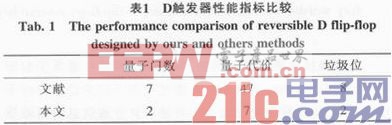

由图3(a)所示,当C输入为0时,输出Q保持不变,当C输入为1时,输出Q和D的信号相同。将图3(a)中的电路封装成图3(b)所示的模块。本文设计的可逆D触发器(图3)的性能指标和文献中设计的可逆D触发器比较如表1所示。

由表1可以看出本文设计的量子可逆D触发器比文献所用的量子门数减少了5个,量子代价减少了40,垃圾位减少了6个。在设计多位脉冲分配器时,量子门数、量子代价和垃圾位会有明显降低。

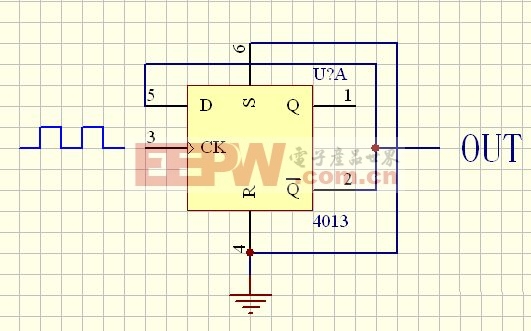

图2所示的计数器是扭环计数器,根据设计原则,将计数器中的触发器替换成可逆D触发器,从而设计出可逆扭环计数器。如图4所示。

尘埃粒子计数器相关文章:尘埃粒子计数器原理 脉冲点火器相关文章:脉冲点火器原理

评论