驱动器 UCC27201 上电时刻 HO 引脚误脉冲的分析及解决

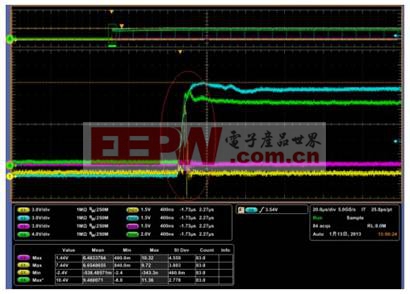

图 4:HO 引脚的误脉冲

2.2 HO 引脚误脉冲的根因分析

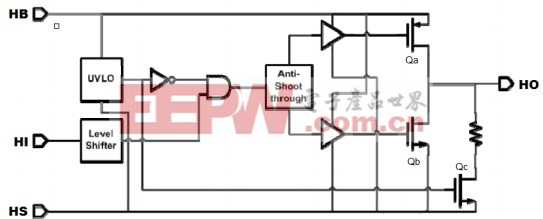

图 5 所示的是 UCC27201 内部与 HO 相关的电路。在 HB 与 HS 之间电压正常建立后,逻辑电路会依据 HI 电平的高或低而打开 Qa 或 Qb,从而实现 HO 高低电平的输出。Qc 是当 HB 与 HS 之间电压还处于欠压阶段时,用以导通以拉低 HO 引脚,确保在该阶段 HO 无输出。

图 5:HO 相关的内部电路

当 HB 与 HS 间电压还处于欠压阶段时,内部电路会产生高电平驱动信号以导通 Qc。但是,该高电平驱动信号的产生存在一定的延时;同时,Qc 设计用来被脉冲信号触发,而非电平信号触发。上述两个因素就造成,当 HB与 HS 间电压上升过快时 Qc 将不能及时导通。此时,如果 HO 被 HB 与 HS 间电压耦合出高电平后(其中一个耦合途径是通过 Qa 和 Qb 的结电容),因 Qc 还未导通,该耦合出的高电平将得以输出,最终形成了 HO 的误脉冲。

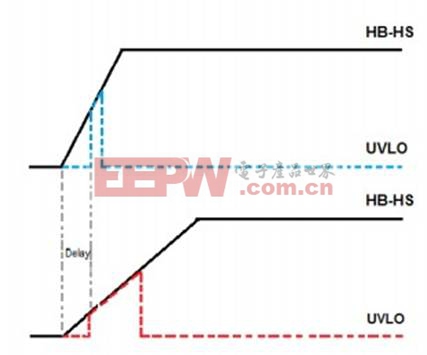

如果 HB 与 HS 间电压上升速率变缓,或者 HB 与 HS 间电压先得以预建立,Qc 的驱动信号(图 6 中的蓝色线和红色线)的高电平脉冲将会变宽,这就能保证 Qc 导通,误脉冲就会被消除。

下文就围绕 HB 与 HS 间电压的上升斜率和预建立这两个方向来讨论,以解决 HO 的误脉冲问题。

图 6: HB 与 HS 电压斜率不同的影响

3、解决措施之增大 Cboot 电容

在相同充电速率条件下,增大 Cboot 电容可以将 HB 与 HS 之间的电压上升斜率变缓,以得到足够宽的高电平信号并使 Qc 导通。

3.1 Cboot 充电过程分析

如图 7 所示,UCC27201 内部有二极管(D1)连接 Pin1 (VDD)和 Pin2(HB)。在 Pin1 的外部连接有供电网络(电压为 12V),电容 Cd(1uF)和串联电阻 Ri(10ohm);在 Pin2 则接有 Cboot 电容。Cboot 电容的充电主要是通过 D1 这条路径完成的。

经过仿真分析(如图 8)知,Cboot 的充电主要包含如下两个阶段:

●阶段一:电容 Cd 通过 D1 给 Cboot 充电。充电电流如图 8 中的红色线所示,先是急剧上升到最大,然后缓慢下降。同时,电容 Cd 的电压(绿色线)逐渐下降,电容 Cboot 的电压(粉色线)逐渐上升。当 Cd 与 Cboot的压差减小为约 0.65V(二极管 D1 的正向导通压降)时,第一阶段结束。

●阶段二:12V 供电电压给 Cd 和 Cboot 充电。受限于 Ri,充电电流将小于 1.2A (12V/10ohm)。

图 8 中的仿真结果是基于 Cboot 为 300nF,图 9 的仿真结果则是基于 Cboot 为 100nF。对比二者知,修改 Cboot电容容量所带来的主要影响是第一个充电阶段的持续时间,分别约为 280ns 和 120ns。下节会分析第一阶段持续时间不同可能会带来的风险。

图 10 给出的是实测波形,其中 CH1 是 LO 的波形;CH2 是 HB-HS 的波形;CH3 是 HO 的波形,CH4 是 VDD的电压波形。可以看到,在 UCC27201 上电后,VDD 电压快速下降,然后又缓慢上升,这与仿真结果一致。

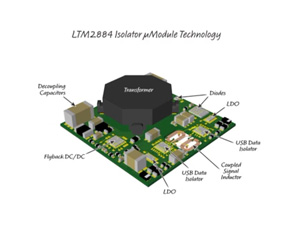

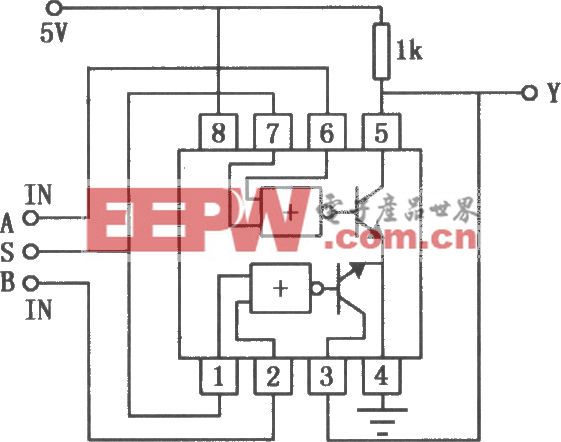

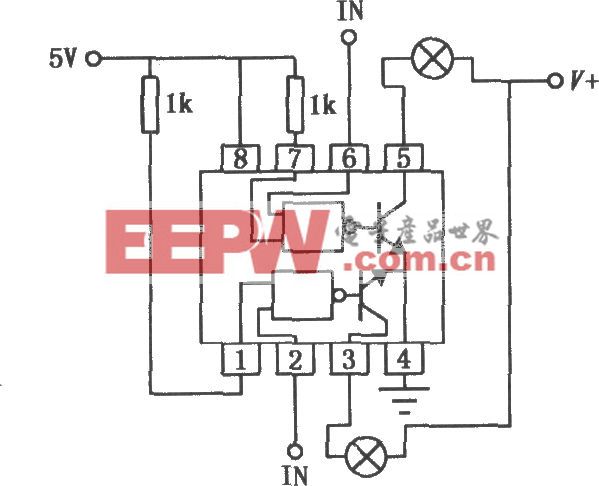

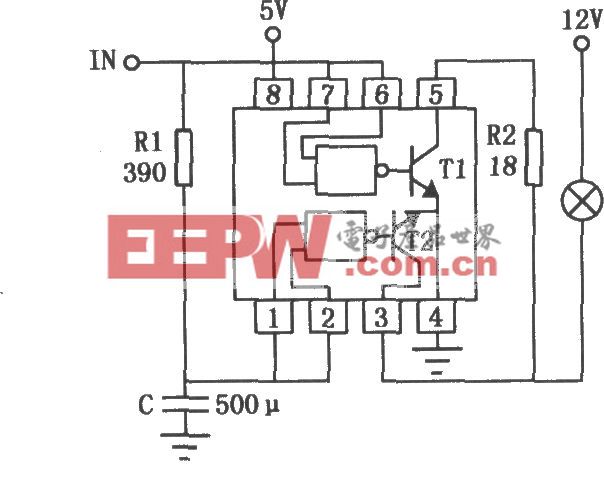

隔离器相关文章:隔离器原理

评论