基于PC104总线的429接口板

3 CPLD内部功能及实现

3.1 开发流程描述

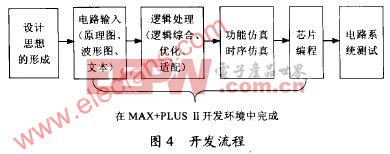

本系统中的CPLD使用Altera公司的MAX7000S系列可编程逻辑器件中的EPM7128SQC100-6型号,从最初的电路设计思想到MAX+PLUSII的波形仿真,再到CPLD芯片编程结束要经过的一般开发流程如图4所示。

3.2 CPLD中的模块设计

本设计中CPLD 的功能是实现ARINC429收发电路与接口板的接口总线PC104总线的数据通信。其功能模块可以分为6部分,以下逐一介绍各模块的功能及其实现的方法。

(1)产生AR1NC429控制器HS3282所需的TTCLK时钟信号模块

TTCLK即发射器时钟信号,本设计中该信号有480 KHZ和1 MHZ两种可选频率,是由一个48 MHZ的晶振提供信号给CPLD,然后由CPLD编程产生480KHZ和1MHZ两种信号以备选择。该模块用图形编辑的方式实现。要产生3282所需要的480KHZ信号需要对输入48MHZ信号进行两次10分频,要产生1 MHZ信号需要对输入信号进行6分频再8分频。6分频电路采用3个JK触发器实现,8分频电路采用74393实现,10分频电路采用7490实现。

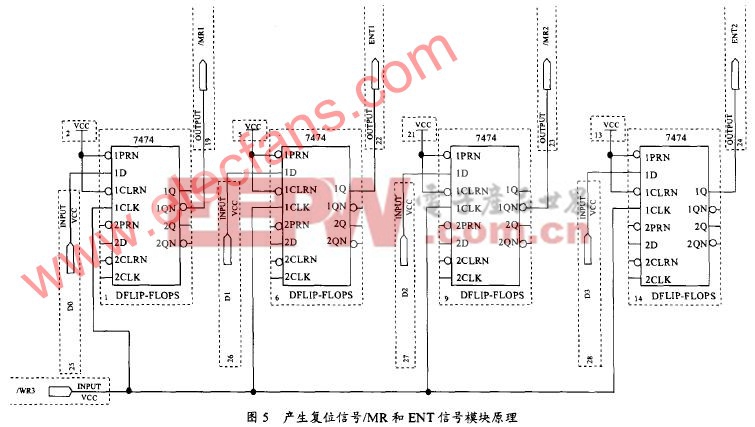

(2)产生复位信号/MR和控制发射器使能信号ENTX的信号ENT模块

/MR是对3282的主复位信号,/MR将直接送到HS3282,而ENT将送到另一模块中,用于控制发射器使能信号ENTX的产生,ENTX=ENT*/TXR,其中TXR为发送缓冲区空标志。该模块也采用电路设计输入方式。其电路主要由4个D型触发器74LS74芯片来完成。输入为总线驱动器的前4个输出,即D0~D3,时钟脉冲为产生HS3282读写信号模块的一个输出信号/WR3,输出为两个HS3282的复位信号/MR1和/MR2以及ENT1和ENT2。本模块具体实现电路如图5所示。

评论