利用CPLD解决便携式产品设计的挑战

举个例子,在莱迪思半导体的ispMACH 4000ZE CPLD中,一个块内的所有I/O引脚都共享一个PowerGuard(针对输入选通,Lattice给予此特性的名称)使能信号,称为块输入使能(BIE)信号。BIE可以用宏单元逻辑在内部产生,也可通过用户I/O从外部源或输入引脚的方式来产生。为增加设计的灵活性,器件有多少块就有多少块输入使能信号,数目从2至16不等。可以把两个或更多的使能信号组合在一起,构成一个用户使能信号。

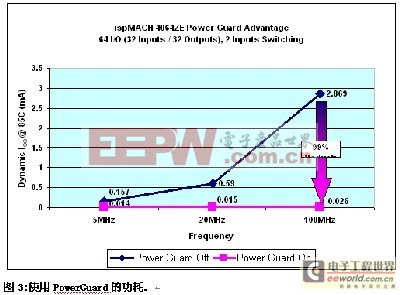

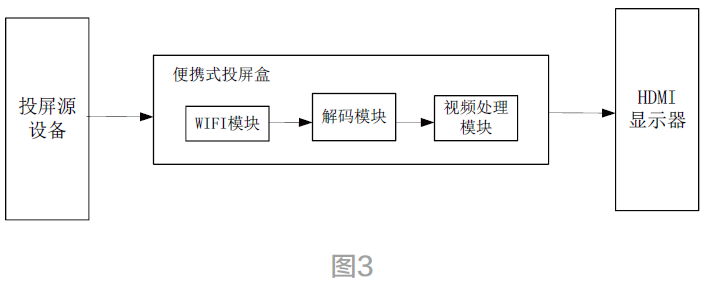

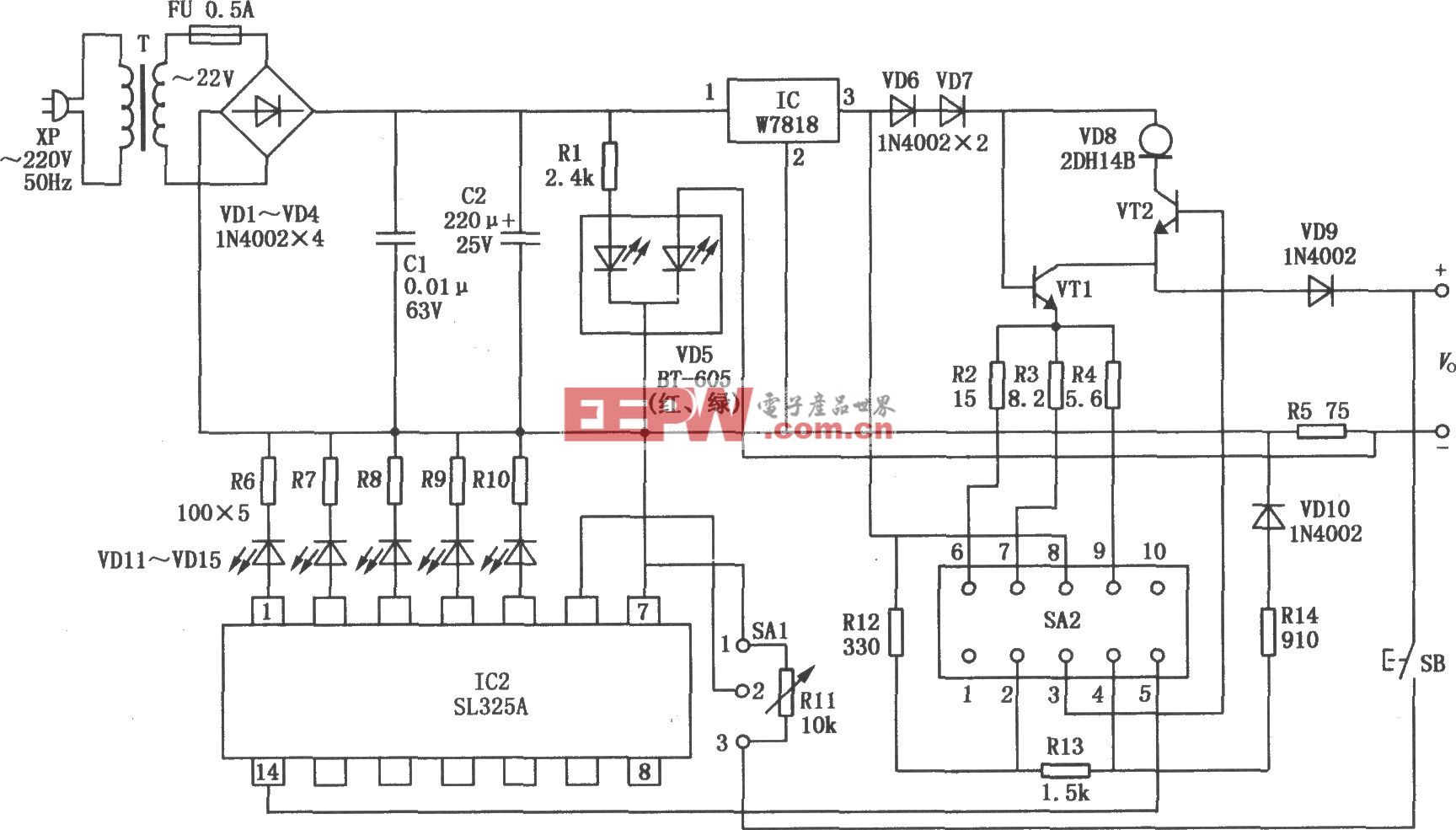

以6宏单元的ispMACH406?ZE器件为例,除了两个激活的输入,其余的都使用了PowerGuard,使动态电流减少了99%。如图3所示,动态ICC从2.9毫安减少至26微安。本文引用地址:https://www.eepw.com.cn/article/166303.htm

有些CPLD可以通过软件对每个引脚单独控制,使其为“高”或者“低”,从而进一步减少I/O电流和系统总功率。电压典型值为250mV~500mV的输入滞后电路通常用来实现降噪和减缓输入信号的变化,以提高信号的完整性。

由于主系统电源的典型值为1.8V,大多数便携式系统都需要LVCMOS接口。这些系统要求能与工作在TTL或LVCMOS标准的其他器件相连接。目前所有CPLD都有独立的核心电压和I/O电压,其中I/O电压能支持1.5、1.8、2.5和3.3V LVCMOS电平。诸如ispMACH 4000ZE这样的CPLD还能够与传统的5V电压LVCMOS器件接口。

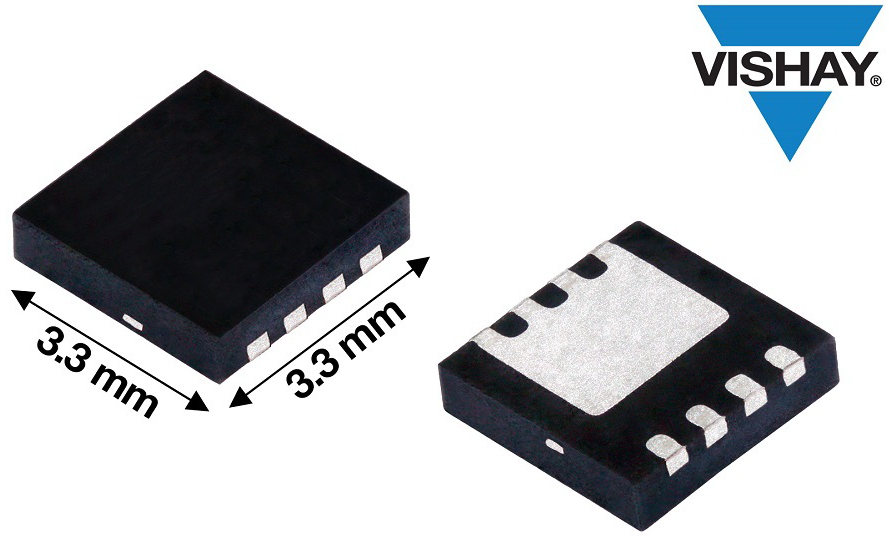

电路板尺寸

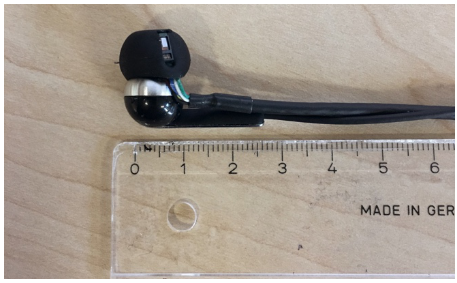

随着便携式产品的体积不断缩小,设计人员必须在非常小的电路板上集成更多的逻辑功能。现在的CPLD可以采用超小型封装,包括芯片级BGA(csBGA,0.5毫米间距),只需25平方毫米或49平方毫米的电路板面积。而传统的薄型四方扁平封装(TQFP封装,0.8毫米间距)封装需要100平方毫米或196平方毫米的电路板面积。

当电路板空间有限时,采用这些封装非常理想。与传统的TQFP封装相比,这些封装使电路板面积减少了75%以上,从而简化了电路板布线并降低整个系统成本。图4为ispMACH 4000ZE csBGA封装示意图。BGA封装的热电阻值(典型值为10度/瓦)比TQFP或PQFP封装更低(典型值20度/瓦至40度/瓦)对于降低功耗和提高器件的可靠性,它们是更好的选择。

p2p机相关文章:p2p原理

评论