如何利用FPGA降低手持设备MPU的功耗

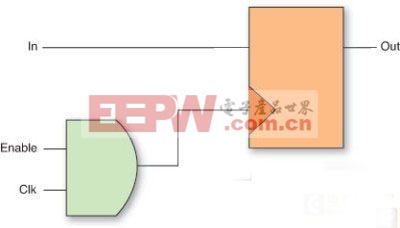

设计人员可以禁用传送到这部分电路的时钟来达到这个目的。一种简单的做法是将时钟信号与使能信号相“与(AND)”,如图2所示。如果使能信号是低电平,那么与门的输出将保持低电平。如果使能信号为高电平,与门将输出时钟信号。

本文引用地址:https://www.eepw.com.cn/article/165671.htm

图2:一种简单的时钟选通机制

还可以使用其它方法。如果可能并且拓扑又支持的话,可以通过复接地址和数据线来减少信号线数量。在我们这个例子中,到视频编码器的输出是16位数据,我们可以把它复接成8位,然后分别在时钟的两个沿(上升沿和下降沿)发送出去。这样做也能节省动态功耗。此外,选择串行接口代替并行接口也能降低功耗。使用带较低电容负载的LVTTL或LVCMOS I/O也很有用。

嵌入式处理器

将处理器嵌入到FPGA中是手持设备设计人员可以采用的又一种策略,它可以带来很多好处。首先,减少了定制处理器带来的上述挑战。其次,外设和处理器之间的交互发生在FPGA内部,因而可以减少I/O数量。由于I/O会消耗相当多的功率,此举也能达到一定程度的节能效果。赛灵思的Virtex-5版本支持PowerPC 440处理器、硬处理器和MicroBlaze软处理器,所有这些处理器都可以被设计人员用来创建高端或低端应用系统。

随着90m和65nm半导体技术的发明,门的尺寸在不断缩小,导致静态功耗问题越来越突出,在对功耗指标越来越敏感的今天,这是一个极具挑战性的现象。由于功耗问题获得了众多FPGA供应商的重视,在这个领域中已出现许多令人兴奋的新技术。低功耗设计将决定一个系统的集成能力有多强,业界也迫切需要将注重功耗的设计技术标准化。

评论