基于DMA控制器的UART串行通信设计

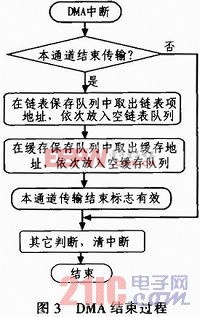

3)DMAx传输完成产生Terminal Count中断,在其中断服务程序中取出FIFO队列UART_LINK_LIST_STORE_TABLE中保存的地址ADDR,将ADDR中的源地址入队到UARTn空缓存队列,然后将ADDR值填充到DMAx的可用空缓存FIFO队列DMAx_LINK_LIST_FREE_TABLE中。流程如图3所示。本文引用地址:https://www.eepw.com.cn/article/160710.htm

3.3 串行数据接收过程实现

UARTn的DMA数据发送过程相对于必送过程较为简单,在配置好相应的寄存器和目标缓存地址后,使能相应DMA通道。当UART接收数据达到触发点后,会触发DMA相应通道的突发请求进行传输。传输结束后,在TerminalCount中断服务中更换目标缓存地址,使能一轮即可。当然在

配置中,DMA通道的突发个数应设置与UART接收FIFO触发点数相同。

4 结束语

在DMA发送进行的过程中,UART_LINK_LIST_STORE_TABLE保存的地址值序列ADDRs中的地址所指空间不能被释放或被其它程序占用,同样的ADDRs中地址的源地址所指的UART缓存空间也不能被释放或被其它程序占用。如果在这个过程中出现了不满足上述要求的情况,则会出现不可预测的错误。

评论