基于VHDL的MTM总线主模块有限状态机设计

3 仿真验证

QuartusⅡ是Altera公司推出的集成开发软件,使用QuartusⅡ可以完成从设计输入、综合适配、仿真到编程下载整个设计过程,Quart usⅡ也可以直接调用Synplify Pro、以及ModelSim等第3方EDA工具来完成设计任务的综合和仿真。

文中利用QuartusⅡ9.0版本软件和Cyclone系列EP1C6Q240C6芯片对所设计的MTM总线主模块状态机的VHDL代码进行了时序仿真和功能仿真,分别如图4、图5所示。本文引用地址:https://www.eepw.com.cn/article/160361.htm

通过波形图可以观察到,该状态机可以很好的实现主状态机的状态转换。当M1输入为“0”时(此时M2、M3为无关状态),MTM总线主模块按照从高到低进行消息传送,直到进入“PAUSE”(暂停状态)然后状态回到“xfer16”(S16)继续进行消息传送;当M1输入为“1”时,主模块无条件进入“waiting”(等待状态);在主模块处于“waiting”状态时若M3输入为“1”状态转入“idle”(空闲状态)再次由高到低位的消息传送。

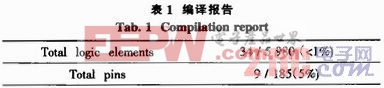

使用VHDL语言描述,语法更为严谨,描述更为清晰简洁;采用“单进程”式状态机描述可以有效地节省FPGA芯片的资源(表1),从而进一步减少功耗,提高系统的稳定性。

4 结束语

文中通过研究MTM总线的基本结构和主从模块间的通讯协议,分析了主状态机的状态转换,并使用VHDL语言设计了该有限状态机,并使用QuartusⅡ开发软件对该状态机进行了仿真和验证,仿真结果表明该程序可以正确描述主状态机的状态转换,该有限状态机使用“单进程”式描述,与“三进程”和“双进程”式相比程序简洁明了并且能够有效地节省资源,减少功耗,提高系统的稳定性。

评论