基于VHDL的MTM总线主模块有限状态机设计

1.2 MTM主模块

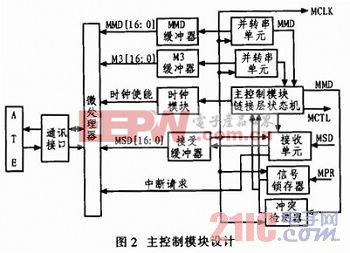

主控制模块设计如图2所示。主控制模块在MTM总线协议中处于主控地位,主要功能是将来自微处理器的数据按照IEEE1149.5标准定义的消息格式进行打包送到指定的从控制模块;同时将来自指定从控制模块的消息包进行解包,并且提取有用数据传回微处理器,供微处理器分析和处理。本文引用地址:https://www.eepw.com.cn/article/160361.htm

主状态机是主控制模块的核心单元,它的作用是控制整个信息传输过程。

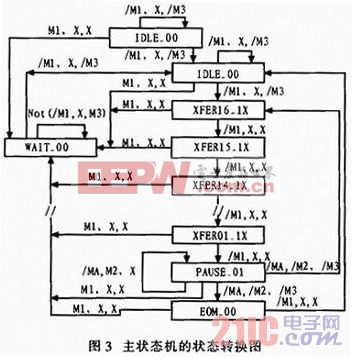

主状态机的状态转换图如图3。当主状态机处于某个给定的状态时,MCTL和MMD信号的逻辑值在MCLK的上升沿产生;在每个MCLK信号周期,主状态机根据控制信号的只发生状态转换;在主状态机的17个传送状态下发送17位的数据包,其他状态不发送数据,同时接收MSD上的数据;在每个数据包发送后,主状态机至少保持在暂停状态不少于4个MCLK周期,若当前接收的MSD数据有效则使接收单元使能信号有效;当主状态机进入结束状态时,当前消息传送结束。

2 基于VHDL的主模块有限状态机的的设计

VHDL主要用于描述数字系统的结构、行为、功能和接口,同时支持层次化和模块化设计,并且可以进行仿真和综合。

数字电路分为组合逻辑电路和时序逻辑电路两种。组合逻辑电路的输出只与当前输入有关,时序逻辑电路的输出与当前输入和过去输入都有关。状态机是一种广义的时序电路,一般包括用于状态译码和产生输出信号组合逻辑和存储状态的寄存器逻辑两部分。

根据MTM总线主模块的状态转换图,其基于VHDL有限状态机的代码如下:

评论