毫米波发射端中频调制的实现

在比较了3种芯片的杂散性能和频率分辨率等性能参数的基础上,可得出AD9857的工作频率最高,由于集成的高速直接数字合成器输出频率要小于系统时钟的43%,因此输出频率范围最大。此外AD9857内部的14位高性能高速数/模转换器,可提高系统的集成度和稳定度。综上所述,本文采用AD9857实现毫米波系统数字上变频。

4 中频调制设计

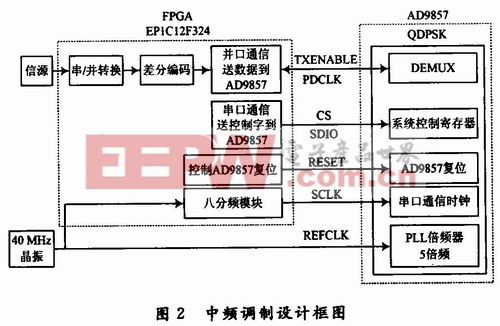

本设计采用基于DDS技术的正交上变频器AD9857与FPGA相结合的方案实现70 MHz中频的QDPSK调制。系统框图如图2所示。本文引用地址:https://www.eepw.com.cn/article/156996.htm

由图2可知,基于EP1Cl2F324的FPGA主要实现基带信号处理、FPGA与AD9857的串口通信、FPGA与AD9857的并口通信和时钟控制设计。

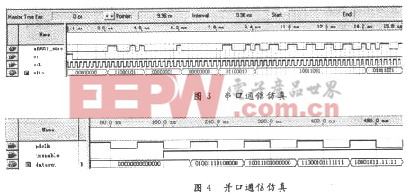

信源首先经串并转换将输入的单路串行数据转换为双路并行数据,经过串并转换产生的数据速率减半,再经过“差分编码”转换为相对码,通过并口送入AD9857进行绝对调相。在FPGA与AD9857串口通信中,当CS为低电平时,开启AD9857的串口,FPGA通过SDIO将控制字发送给AD9857,设置AD9857的工作方式,当CS为高电平时,关闭AD9857的串口,串口通信仿真如图3所示。在FPGA与AD9857的并口通信中,当TXEN-ABLE为高电平时,通过PDCLK读取FPGA中的14位并行数据送入AD9857,当TXENABLE为低电平时,关闭AD9857的并口,并口通信仿真如图4所示。

40 MHz晶振为EPlCl2F324提供系统时钟;经FPGA八分频后通过SCLK送入AD9857中,作为串口通信时钟;经AD9857内部PLL倍频器五倍频后,作为AD9857的内部系统时钟。

AD9857工作在正交调制模式,14位并行I/Q数据分成两路交替输入,经过CIC滤波器,可编程内插器后送人正交调制器。DDS核产生正交本振信号到正交调制器,分别与I/O信号相乘后相加或相减,产生正交调制信号。最后通过14位DAC转变为正交调制的模拟信号输出。

5 结语

采用AD9857和FPGA相结合的方法实现了中频调制,由于AD9857采用了直接数字频率合成技术,消除了由模拟调制所引起的相位、增益的失衡和交调失真。该设计简化了系统结构,降低了成本,提高了系统的性能和可靠性。同时提出了一种采用两次变频的上变频方案,此方案降低了毫米波滤波器的设计难度,减弱了功率放大后的强发射信号泄漏对发射机性能指标造成的影响。

评论