集成计数器74LS161的逻辑功能扩展

由图2,图3可知,将加法计数器状态图中每一状态中各位取反即为减法计数器的状态图。

以可编程计数器74LS161的状态输出Q3,Q2,Q1,Q0为变量并增设一个加/减控制变量M进行逻辑修改设计,在M=0时各位状态输出不变,计数器进行加法计数;在M=1时各位状态输出取反,计数器进行减法计数,设修改设计后的计数器的状态输出为

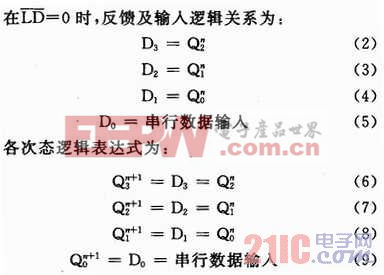

由表2可得逻辑修改后的状态输出逻辑表达式为:

![]()

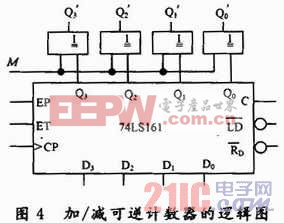

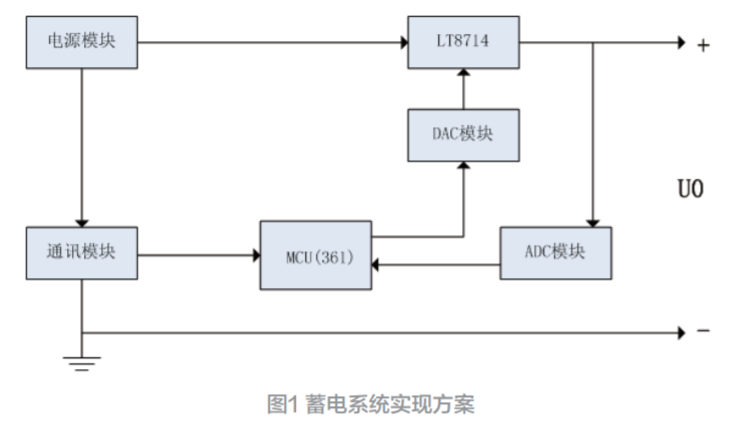

图4为按式(1)构成的加/减可逆计数器的逻辑图,其中,C在加法计数时为进位输出、在减法计数时为借位输出。

1.2 可编程计数器74LS161扩展构成移位寄存器

将可编程计数器74LS161的状态输出反馈到预置数输入端,实现“次态=预置数”的时序关系,可构成移位寄存器电路。

评论