基于ARM+FPGA架构的三维图形加速系统

本文选用S3C2410嵌入式处理器和Cyclone II系列FPGA实现图形加速以及其他功能模块,辅以LCD屏、串口等外围电路实现整个图形系统。

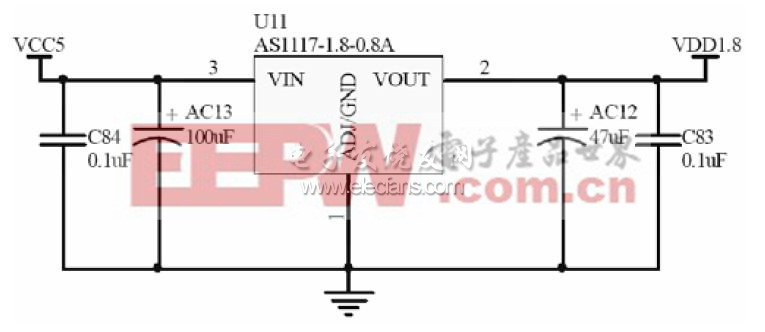

电源设计

本系统需要多个不同电压值的直流电源供电,包括5V、3.3V、1.8V和1.2V。其中5V电源从外部直流电源直接引入,而其他电压值则由5V电压变换得到。

S3C2410的内核电压为1.8V,外部I/O和存储器电压为3.3V。系统选用低压差稳压器AS1117实现这两种电压的转换,固定输出时只需三个引脚,如图3所示。

图3 1.8V电源电路

本文使用TPS70345为FPGA提供1.2V内核电压和3.3V IO电压。

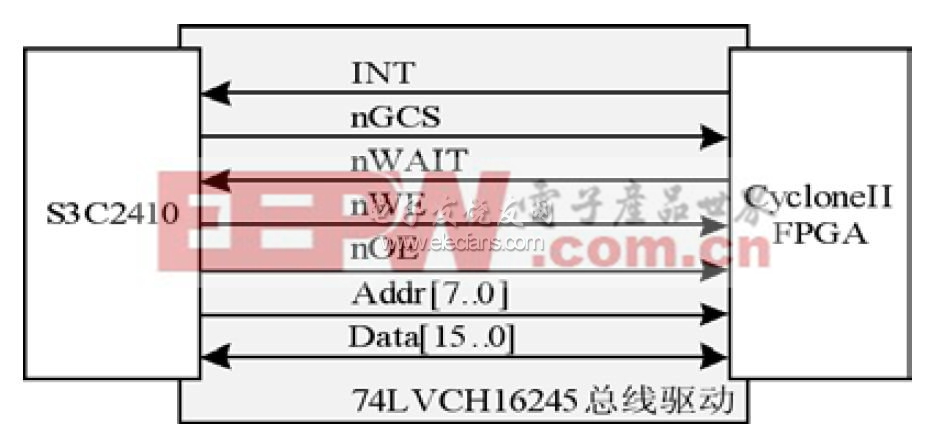

生成三维图形时,嵌入式微处理器上运行的图形应用程序生成三维图形的渲染列表,并将渲染列表写入到FPGA的渲染列表缓冲区中,等待图形加速模块的处理。ARM与FPGA接口电路既要保证可以完成渲染列表的写操作,又要能够对FPGA中总线接口模块、图形加速模块、LCD控制器等的内部寄存器进行读写操作。接口电路如图4所示。

图4 ARM与FPGA接口电路

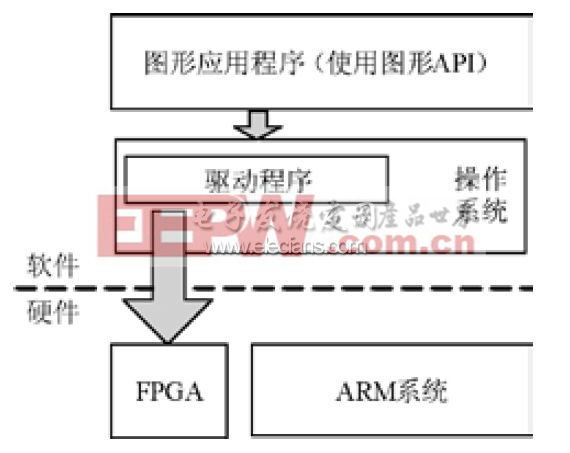

系统软件设计

系统软件架构

本文使用FPGA实现整个三维图形处理流水线,由硬件完成三维图形生成和处理。运行在操作系统上的图形应用程序通过调用图形API实现具体应用,而驱动程序将图形API的调用转换成渲染列表,从而将具体的三维图形处理任务交给硬件完成,如图5所示。

图5 系统软件架构

考虑到嵌入式图形系统除了进行三维图形处理之外,还应当能够为用户提供友好的用户图形操作界面,本文采用了Windows CE操作系统。

评论