串行RapidIO在WiMAX基站系统中的应用

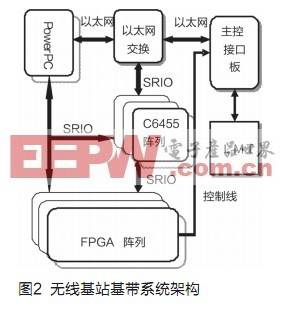

图2所示系统是基于CPU的高性能DSP系统。PowerPC主要针对无需大量乘法运算的一般应用,如MAC层处理。DSP主要完成滤波、矢量乘法和查找以及图像或视频分析等信号处理操作。FPGA实现FFT或者PAPR算法等。

本文引用地址:https://www.eepw.com.cn/article/101030.htm

图2所示的无线基站基带系统具有极高的灵活性和可扩展性,在这种架构中,各个处理器的任务分工具有很大的灵活性。由于架构已经不再与运算密切相关,流量和处理能力可在运行时间内从一个器件转移到另外一个器件。该架构也具有可扩展性,有助于满足具体应用在性能和成本方面所需的端点数量增减。例如,可以轻易改变 DSP型号和 DSP 数量,以实现相同的设计可以匹配到从微蜂窝到大型基站的设计要求。要在降低成本同时满足更高性能和带宽,关键在于采用模块化和基于标准的架构。构建下一代基带卡和基于连接了多个DSP、FPGA 和 ASIC 的串行RapidIO 接口的结构型架构具有许多优势。

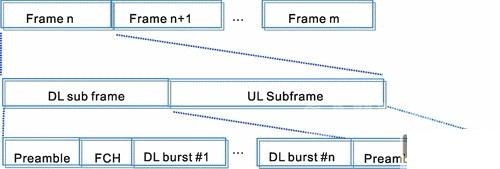

系统在WiMAX BBU中的应用

·WiMAX BBU系统架构

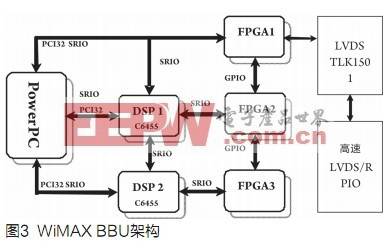

图3是基于图2的WiMAX BBU系统,该系统硬件上包括一片PPC处理器MPC8548,两片DSP处理器(TI的C6455)和三片Xilinx FPGA V5LX110。FPGA与DSP之间使用SRIO口通信,DSP与PPC之间使用PCI接口和SRIO进行通信,FPGA之间使用仿PCI接口进行通信。DSP1与DSP2之间使用SRIO接口进行通信。

本系统中还保留PowerPC与DSPC6455的PCI32互连,这样有利于boot模式下程序的下载。FPGA1主要实现IFFT和PAPR算法;FPGA2主要实现RANGING和FFT算法;DSP1主要实现信道编码、调制、空时编码和子载波映射,DSP2主要实现信道解码、解调、信道估计和子载波解映射。FPGA3主要实现TURBO的解码。另外MIMO的上行算法会在DSP2、FPGA2和DSP1上协同处理。

评论