英特尔Meteor Lake: Tile设计+台积电制程,大有看头

来源:Technews

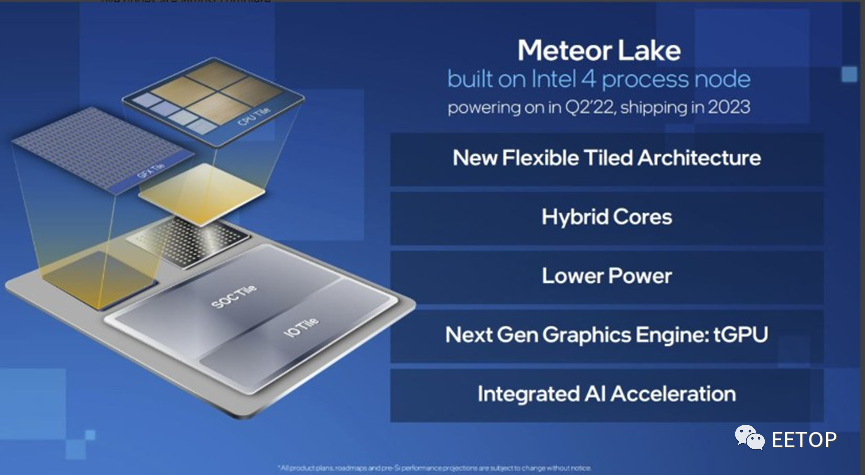

尽管英特尔(Intel)今年第一季的财报表现不亮眼,毛利率跌至史上新低的36.4%,但其公布了更多有关Meteor Lake CPU的细节,其中首次采用Tile架构和使用竞争对手台积电的制程让人眼睛一亮,产品大有看头。

Meteor Lake制程亮点

其实Tile架构和台积电制程都不是新玩意儿,但对英特尔来说都是全新一页。Tile架构类似AMD已使用多年的Chiplet架构,有别于传统的大型单一芯片(Monolithic)设计,Tile架构的处理器上有多个芯片分别负责不同功能如CPU、I/O、显示输出和快取存储器。

这样的好处是各芯片可以采用不同的制程,进而降低成本以及加速芯片的推陈出新。举例来说,英特尔之后只需要集中火力在CPU Tile的架构和制程创新,I/O和快取内存这些比较不需要先进制程的单元则可以采用较成熟的制程以降低成本。

另外也带出了Meteor Lake的另一个亮点,便是采用了台积电的制程。显示单元采用了台积电的5纳米制程,SoC(芯片组)和IOE Tile则是采用了更为成熟的6纳米制程。这也间接证明即便是最大的竞争对手也认可台积电在成熟制程的稳定性和成本优势。

但最主要的CPU Tile还是采用全新英特尔架构和Intel 4制程。Intel 4制程的晶体管密度约介于台积电的N5和N3制程之间,加上首次采用EUV(极紫外光刻),预料可以扭转长久以来在制程上的劣势,产品的能耗比也能追上最大的竞争对手AMD甚至苹果。

Meteor Lake的CPU Tile选择

不只采用全新架构和竞争对手制程,Meteor Lake也会首次采用Intel 16制程的3D Foveros封装技术。3D Foveros的概念有点像AMD的3D V-Cache,底部有一个基底晶圆(Base Die),透过Foveros连接技术可以在这个基底晶圆上堆叠处理器的各个单元。

如此一来便可以依照客户需求建构出更多元的产品,架构和制程转换的成本也会降低。英特尔也预告之后的Arrow Lake甚至是Lunar Lake都会采用这个封装技术,这也意味着对制程需求较低的I/O或显示单元有可能会持续和竞争对手台积电合作,采用相对更成熟的制程。

总结来说,Meteor Lake采用类似AMD Chiplet的Tile架构,将原本整合全部功能的大型单一芯片依照功能不同切割,并依照各功能需求采用不同的架构和制程,能够有效降低更新成本。不仅如此,相较于竞争对手全部仰赖台积电制程,Meteor Lake的CPU Tile仍然采用英特尔自家制程,而且是首次踏入5纳米以下的Intel 4,搭配全新架构,下半年即将推出的Meteor Lake会有多少效能和效率提升,令人期待。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。