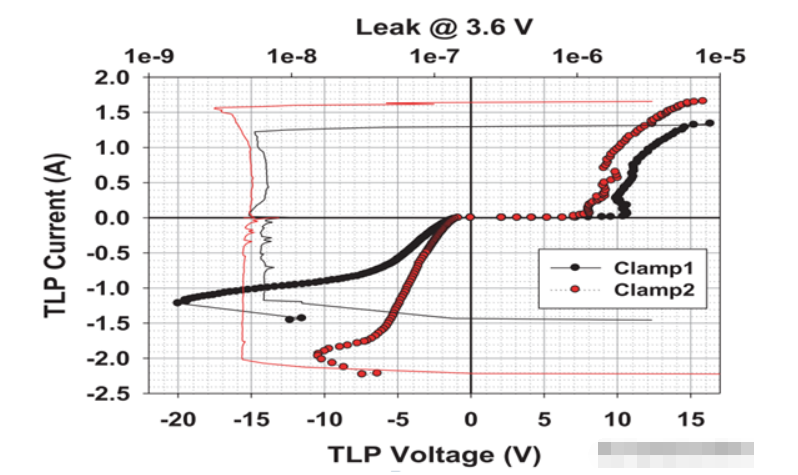

-通过电压/电流曲线分析,深入了解静电放电防护组件(ESD Protection Device)之物理特性。

-在芯片制作完成之初,即能先预测产品之静电放电的承受能力,以增加产品的研发效率。

-重视HBM ESD pulse所造成的IC失效模式及电性行为。

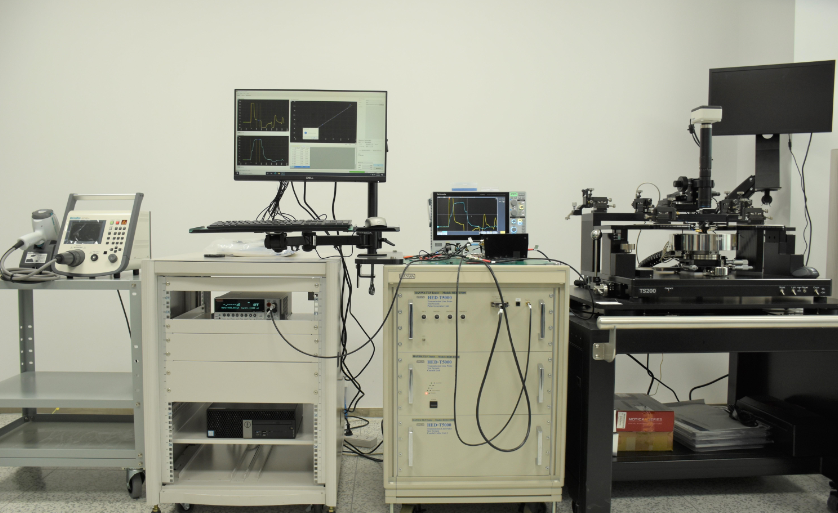

Nomal TLP

VF TLP

TLP测试系统

电性栓锁测试用来评价CMOS ICs对噪声或者瞬时的免疫程度 (Immunity of transient induced due to external noise or internal under/over-shoot)。栓锁效应是一种在CMOS、Bipolar或BiCMOS里p-n-p-n 4 层SCR架构的寄生电路(Parasitic circuit)n所造成的影响。

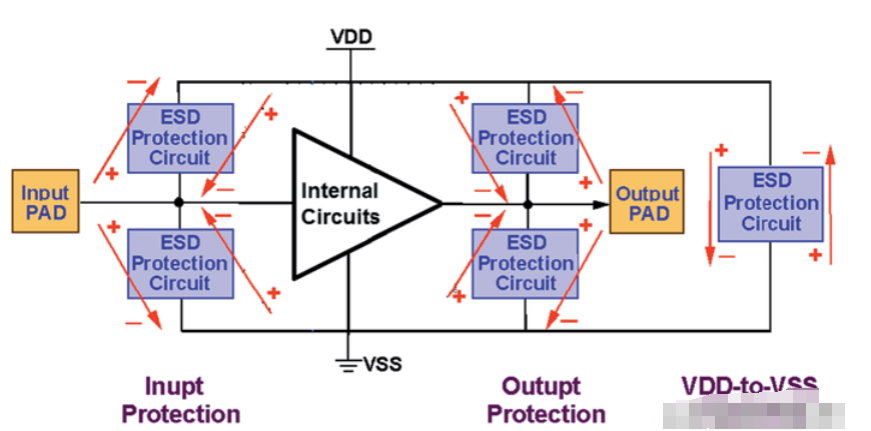

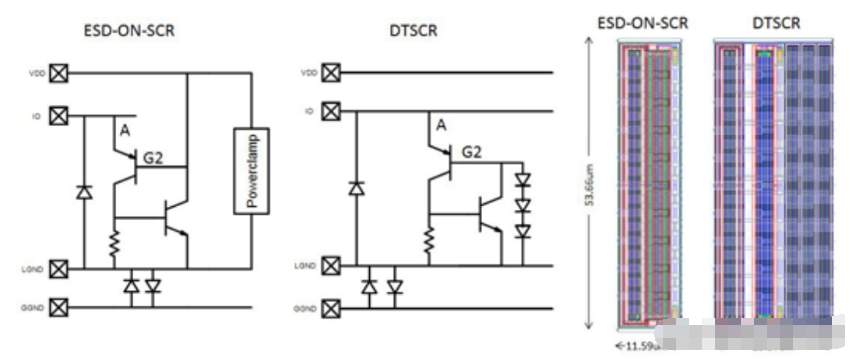

ESD/Latch-up保护电路设计ESD /电性栓锁测试服务之外,平台同时提供ESD I/O库、ESD/电性栓锁电路设计咨询、以及客户电路布局的详细分析,由此协助客户的芯片或产品达到最佳的ESD/电性栓锁防护能力。