ARM+FPGA+DSP,这个开发板有点牛!!!源码还公开了,赞!

说起开发板,一般有条件的公司都会直接从原厂拿demo,不过这种通常数量很有限。要是想用开发板或者是核心板直接做量产产品,从原厂就不可能了。好在也有一些厂家做开发板做得不错,比如我之前有推荐过的创龙科技。

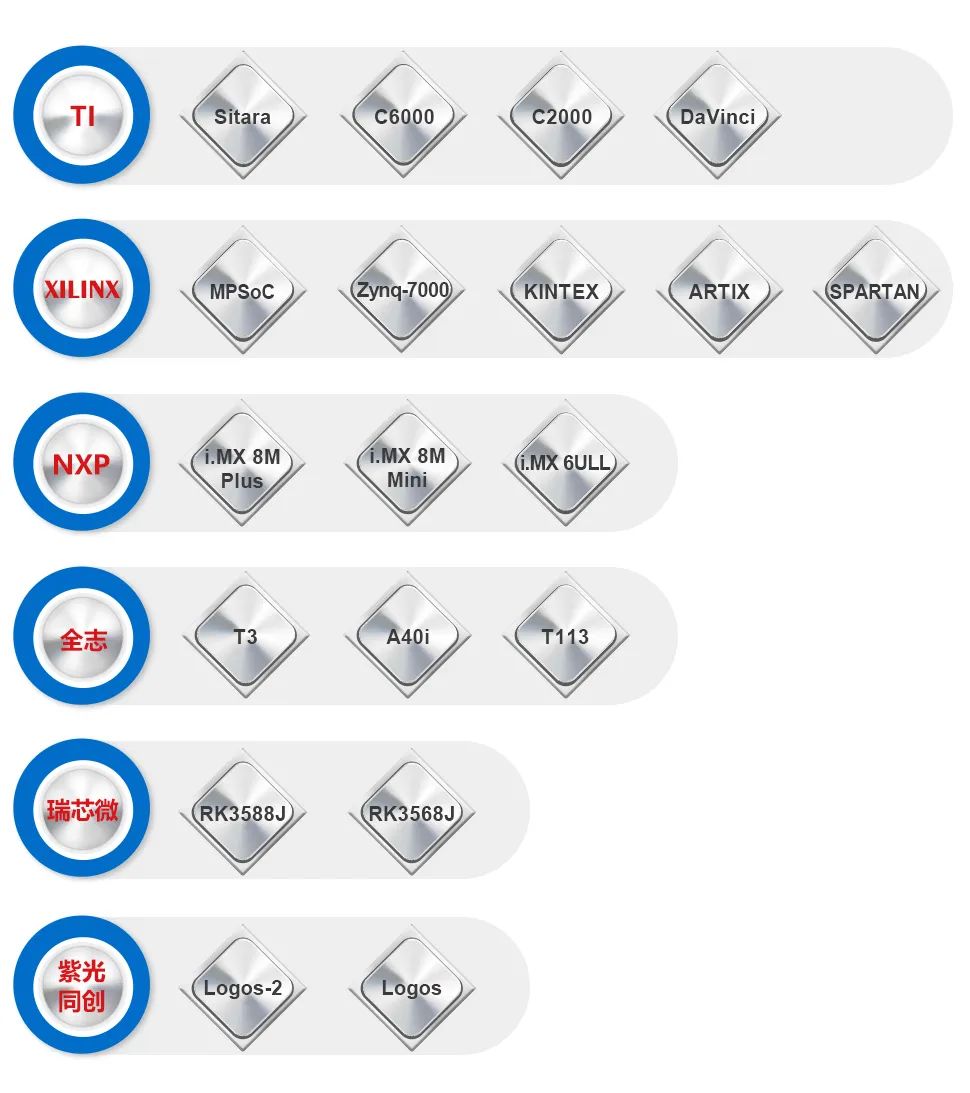

创龙科技有各种开发板/核心板,包括TI、Xilinx、NXP、全志、瑞芯微、紫光同创等厂商处理器平台,产品广泛应用于工业自动化、仪器仪表、能源电力、通信、医疗、安防等行业。

非常的全面,不论是自己玩,还是公司开发产品,如果要用到,都可以去看看。最近呢,创龙又新出了一个开发板,我看了下,有点牛,下面介绍给大家。

本文分享性能超强的ARM+FPGA+DSP异构多核开发板——TMS320C6678 + Zynq-7045的三大经典案例,案例源码免费下载,下方查看详情!

(1)基于SRIO的ZYNQ+DSP核间通讯案例(2)基于CameraLink、SDI、PAL的目标追踪视觉方案(3)基于AD9361软件无线电方案

案例源码限时公开,长按下方二维码下载!

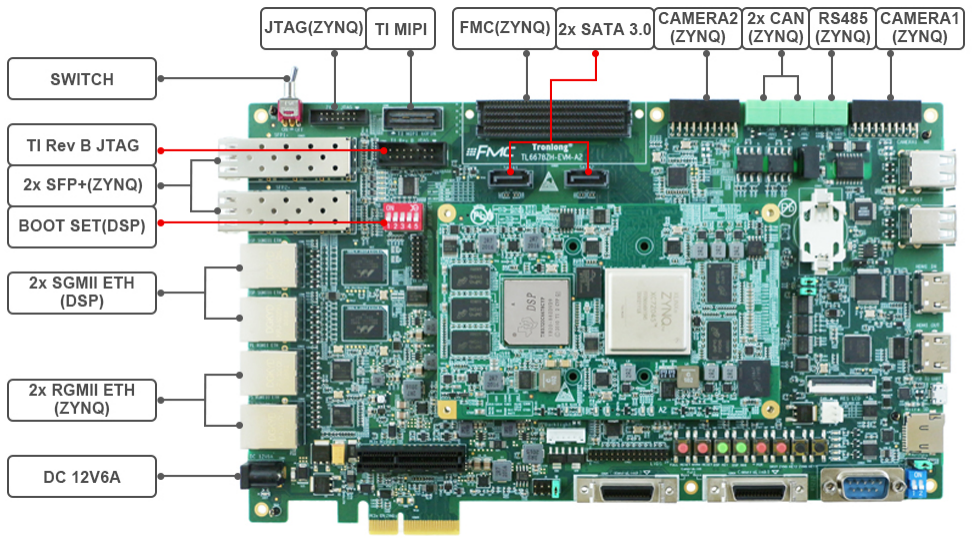

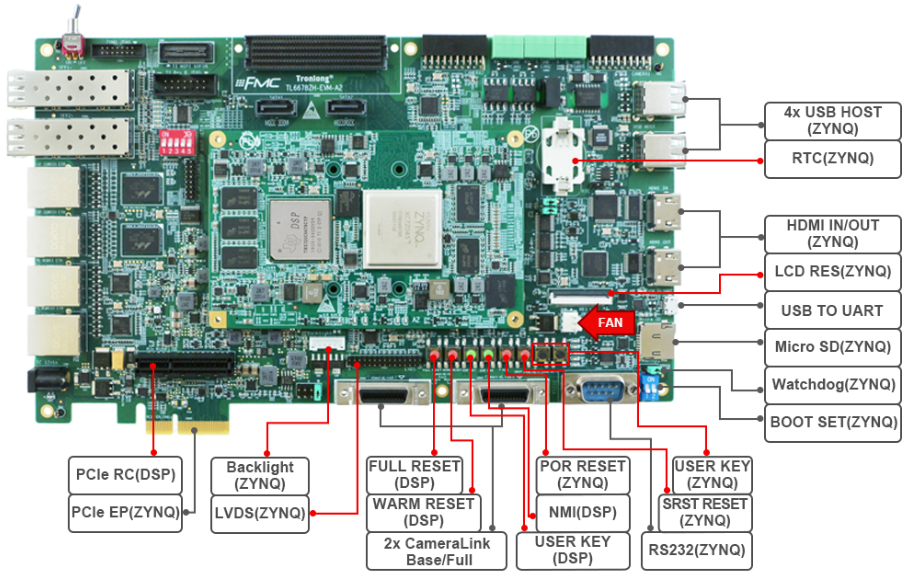

开发板简介

TL6678ZH-EVM开发板基于TI KeyStone架构C6000系列TMS320C6678八核C66x定点/浮点DSP,以及Xilinx Zynq-7000系列XC7Z045/XC7Z100 SoC处理器设计。

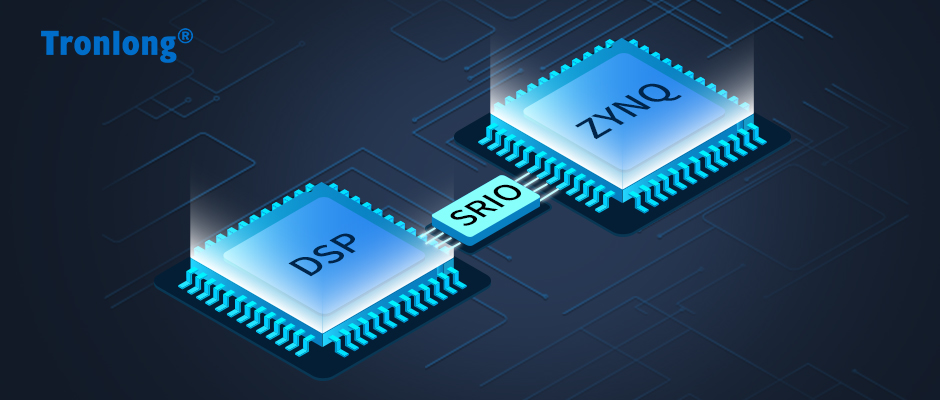

TMS320C6678每核心主频可高达1.25GHz,XC7Z045/XC7Z100集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源。核心板内部DSP与ZYNQ通过SRIO通信总线连接。

开发板接口资源丰富,引出双路CameraLink、双路SFP+光口、四路千兆网口、双路SATA、双路PCIe、四路USB、双路CAN、双路CAMERA、HDMI IN/OUT、LVDS、LCD、RS485、RS232、Micro SD、HPC FMC等接口,方便用户快速进行产品方案评估与技术预研。

案例一:

基于SRIO的DSP+ZYNQ核间通讯案例

图 4

注:详细案例说明,复制链接打开:https://mp.weixin.qq.com/s/GixmZd-2aAxYtSvQhzIxhg

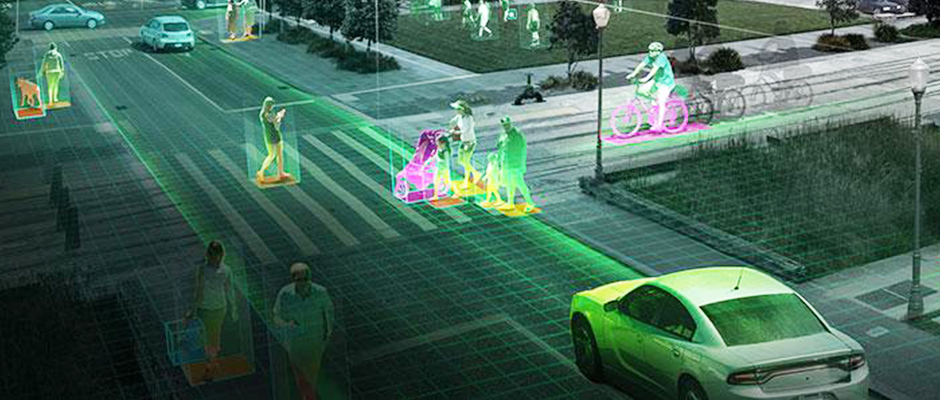

案例二:

基于CameraLink、SDI、PAL的目标追踪视觉方案

注:详细案例说明,复制链接打开:https://mp.weixin.qq.com/s/3iB-CiecfxpgogUjvCulkg

案例三:

基于AD9361软件无线电方案

图 6

备注:此案例源码需购买开发板+AD9361模块方提供。如需购买开发板+AD9361模块,请与我司联系。

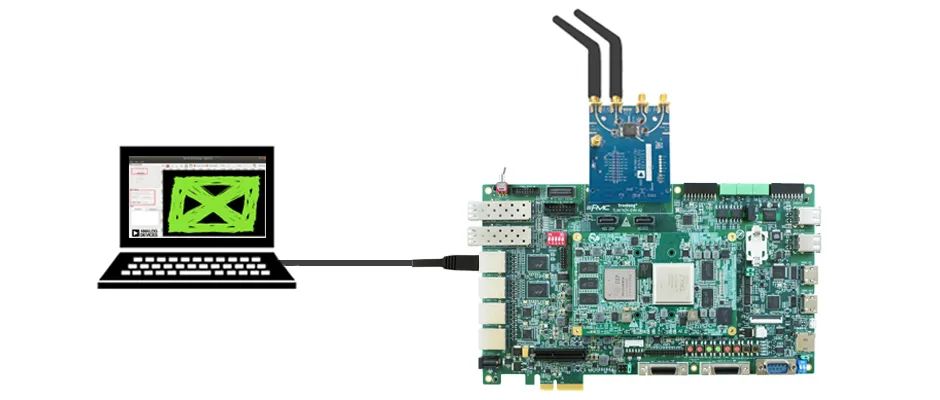

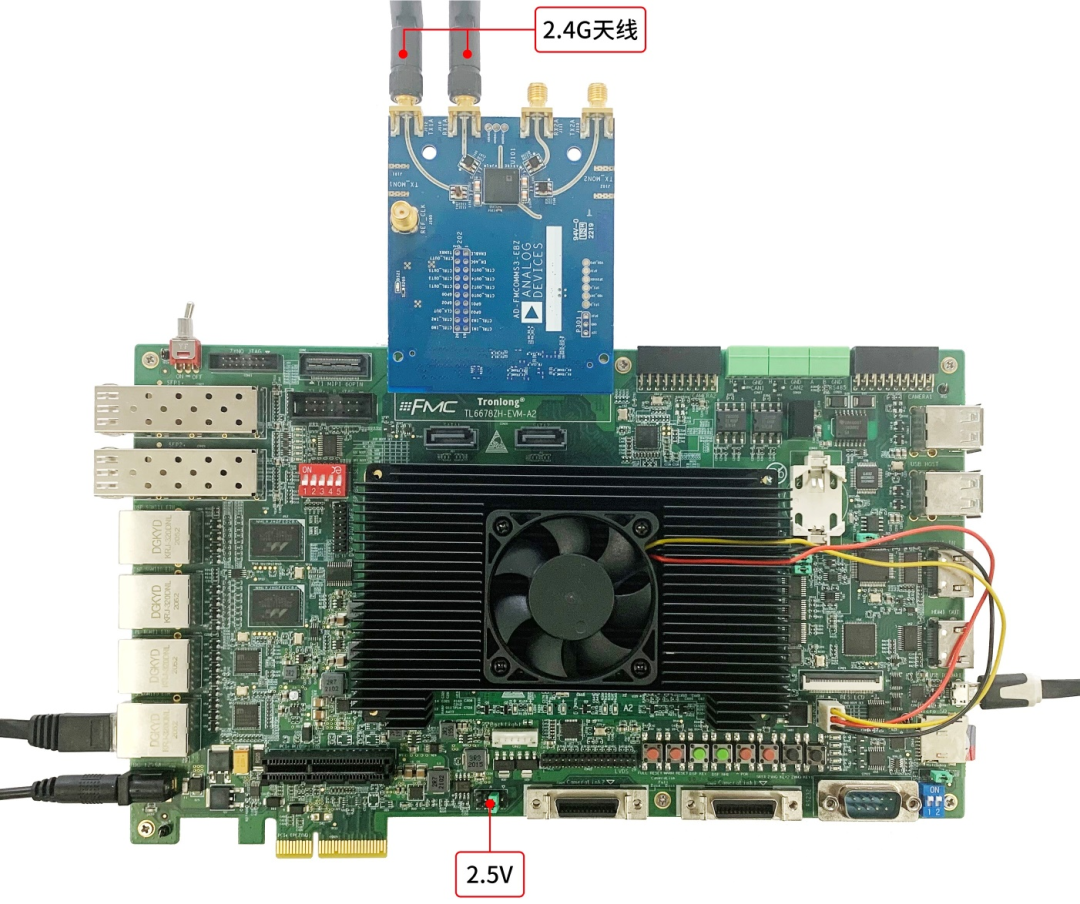

1.案例说明

本案例基于ADI AD9361模块AD-FMCOMMS3-EBZ和创龙科技TL6678ZH-EVM开发板搭建AD9361 RF(Radio Frequency)收发测试平台,实现QPSK(Quadrature Phase Shift Keying)数字调制和FM(Frequency Modulation)收听。AD-FMCOMMS3-EBZ模块开发官方参考链接:https://wiki.analog.com/resources/eval/user-guides/ad-fmcomms3-ebz。

2.案例测试

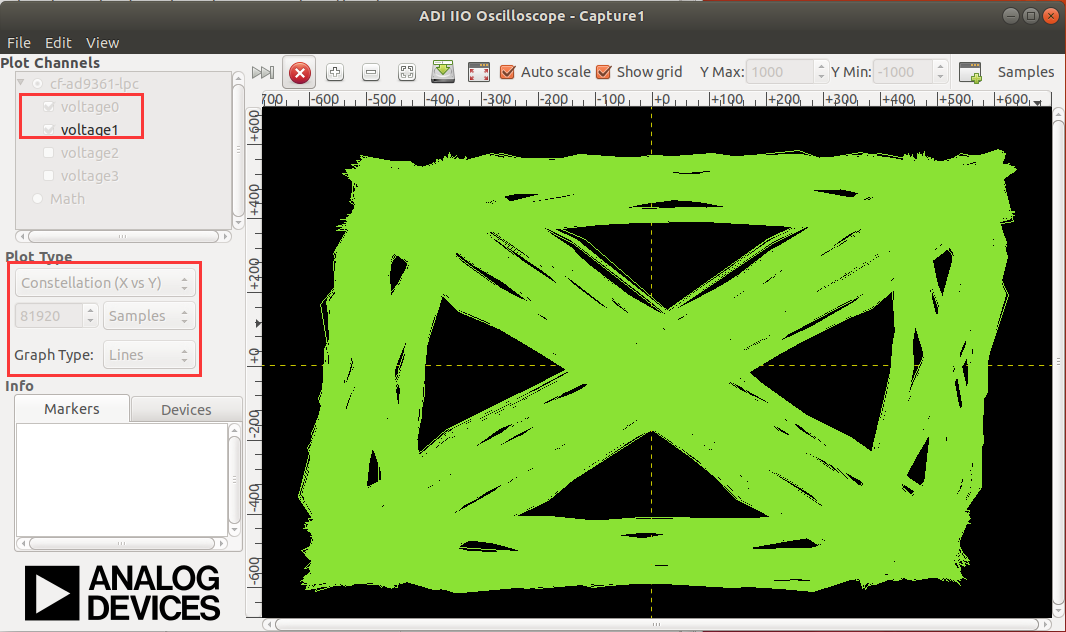

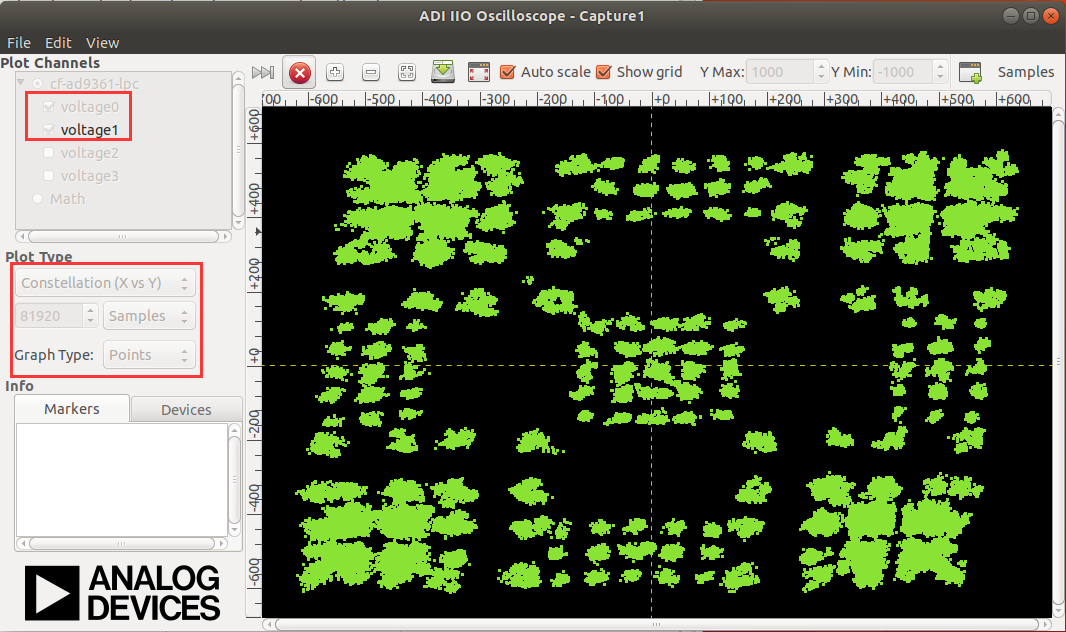

2.1 QSPK数字调制测试

请将AD-FMCOMMS3-EBZ模块的TX1A、RX1A分别连接2.4G天线,并将模块连接至开发板FMC接口,开发板J1跳线帽选择2.5V档位,以配置FMC IO的BANK电压为2.5V,同时使用网线将开发板PS RGMII0 ETH网口和Ubuntu上位机连接至同一个路由器。

(1)线状形式星座图a)Plot Channels勾选voltage0和voltage1。b)Plot Type选择Constellation(X vs Y),设置81920个采样点,设置Graph Type类型为Lines。c)点击

启动数据显示。

启动数据显示。

(2)点状形式星座图a)Plot Channels勾选voltage0和voltage1。b)Plot Type选择Constellation(X vs Y),设置81920个采样点,设置Graph Type类型为Point。c)点击

启动数据显示。

启动数据显示。

2.2 FM收听测试

请将AD-FMCOMMS3-EBZ模块的RX1A连接FM天线,并将模块连接至开发板FMC接口,开发板J1跳线帽选择2.5V档位,以配置FMC IO的BANK电压为2.5V,同时使用网线将开发板和Ubuntu上位机连接至同一个路由器。将USB声卡连接开发板USB HOST接口,并将耳机连接USB声卡的音频输出端。

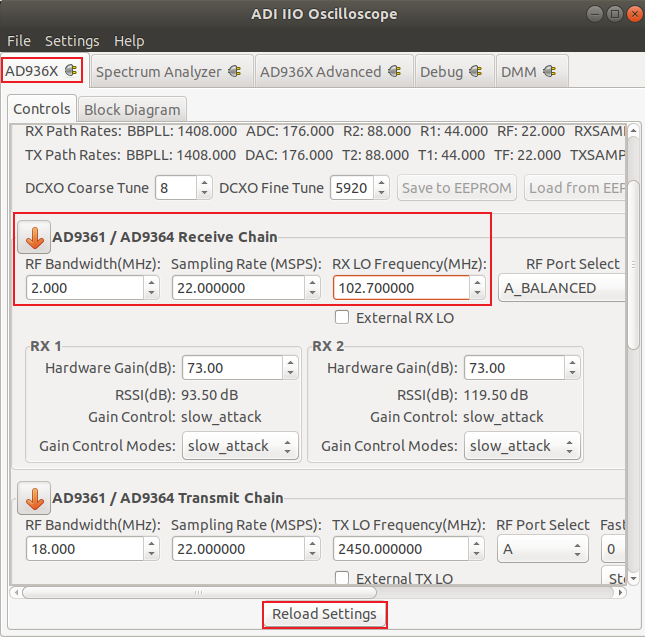

请按照如下方法,配置AD9361的接收链路。(1)设置RF Bandwidth为2MHz。(2)设置Sampling Rate为22MSPS。(3)设置RX LO Frequency为102.7MHz。(4)点击"Reload Settings"加载配置。

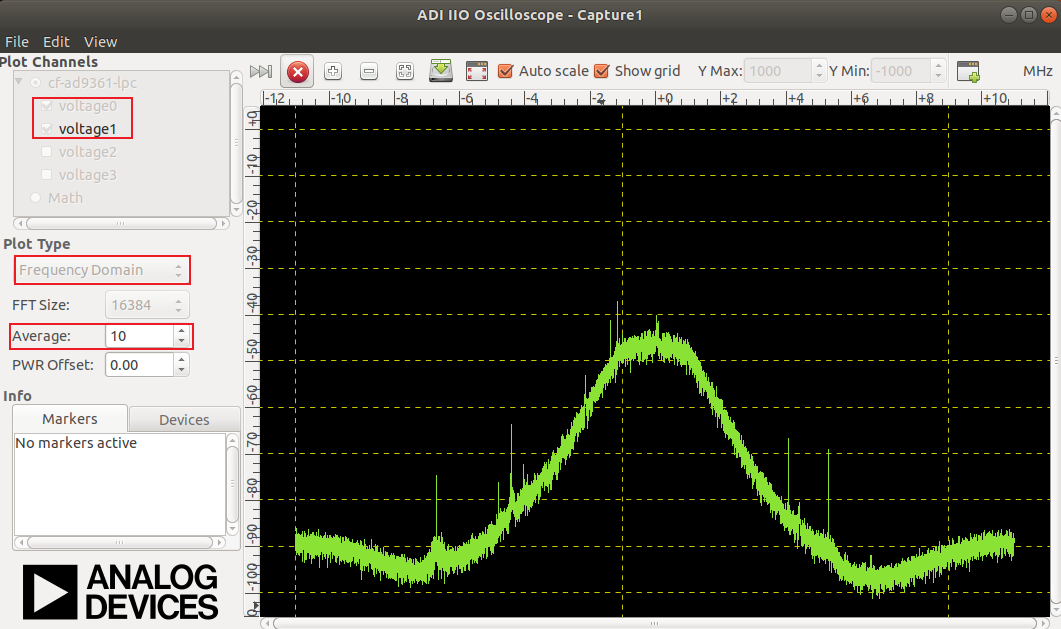

请按照如下方法,进行AD9361 RX 1的数据接收查看。(1)Plot Channels勾选voltage0和voltage1。(2)Plot Type选择Frequency Domain。(3)Average设置为10。(4)点击

启动数据显示。

启动数据显示。

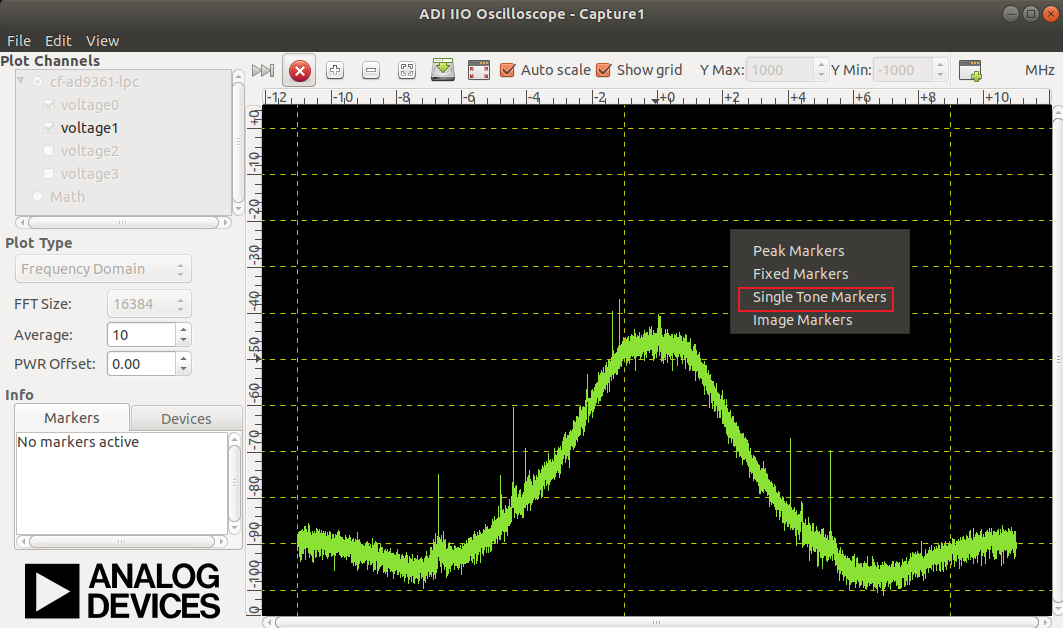

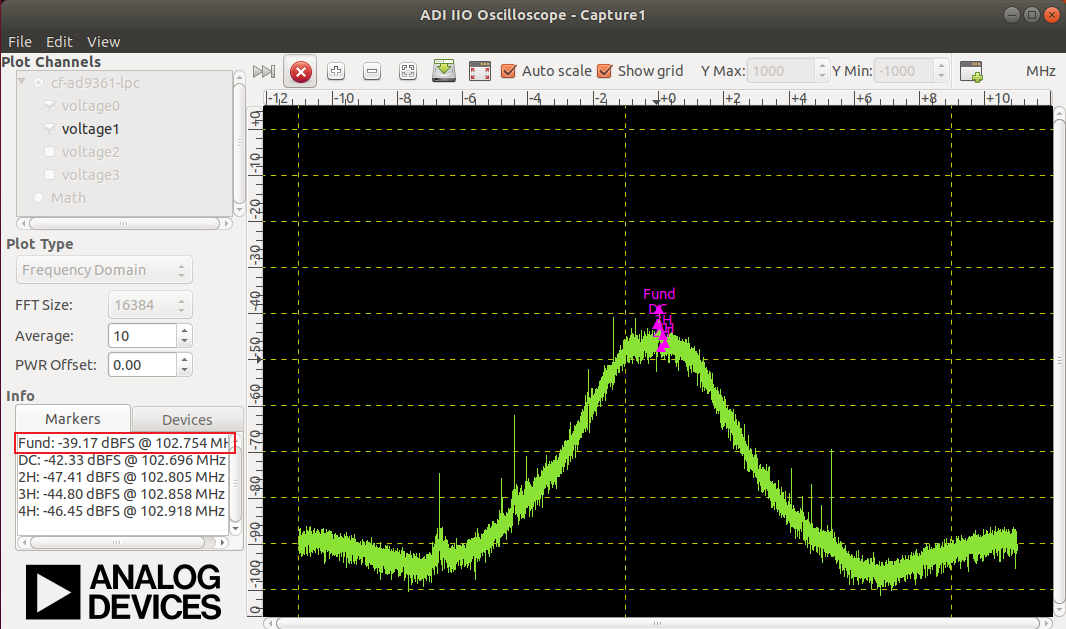

在频谱显示区域右键选择"Single Tone Markers",可在左侧Markers窗口查看当前FM收听频点。

更多推荐TMS320C6678 DSP技术交流QQ群:79635273、332643352ZYNQ技术交流QQ群:193393878、645235672Kintex-7 FPGA技术交流QQ群:311416997、101245165

关于创龙科技

官方合作伙伴

产品线

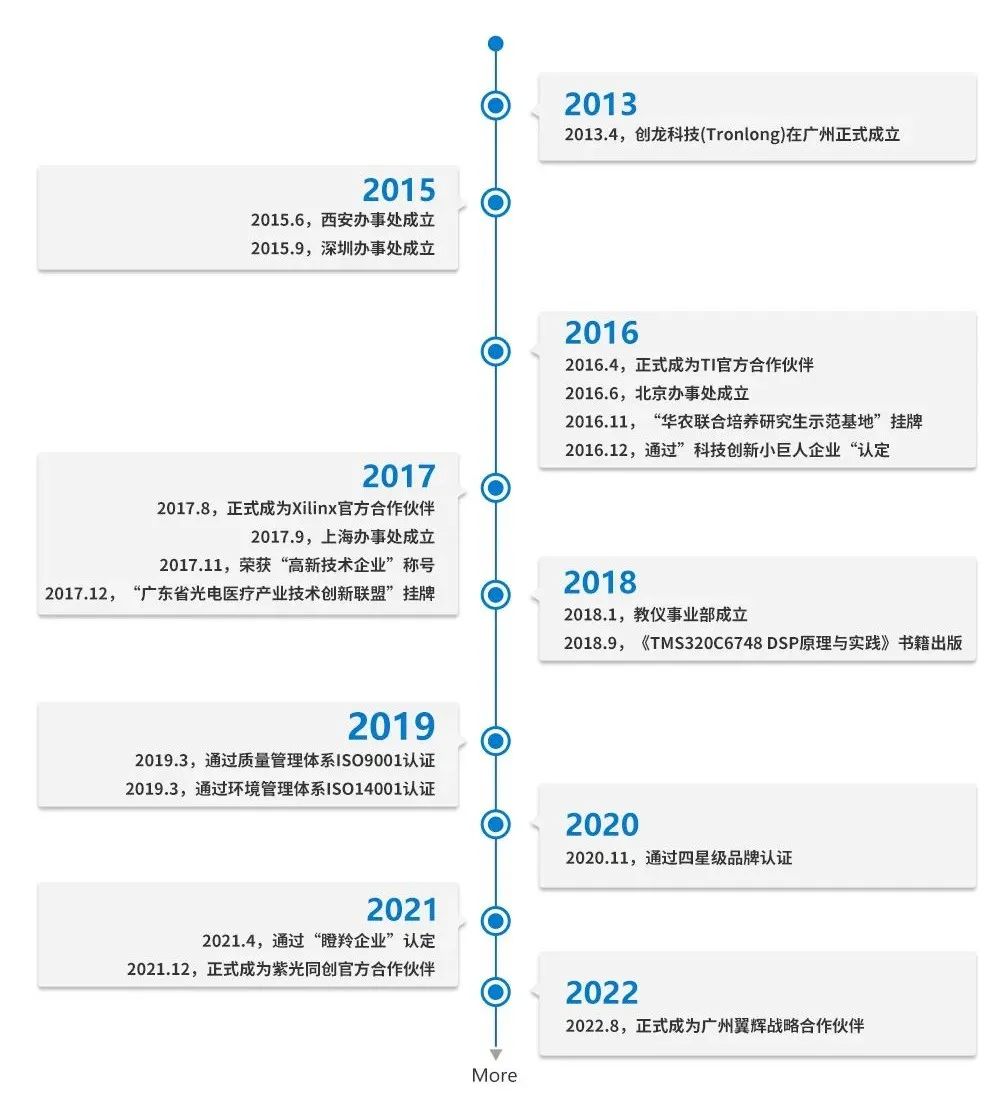

发展历程

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。