高密度互连(HDI)技术远不止电路设计的小型化。它代表着我们行业的重大突破。作为《快乐的霍尔顿》的作者人类发展指数手册HDI打破了传统的“以同样的方式,只不过更小”的传统方法。HDI的进步不仅改善了元件连接的尺寸和几何结构,还改变了器件本身的电性能,从而降低了功耗,提高了性能。

在现代水平上实施HDI涉及到在材料、成像、装配、测试和设计方面做出改变。本文研究了这些变化,并展望了在不久的将来我们可能看到的情况,因为HDI将继续改变我们看待复杂、紧凑的电路以及它们使之成为可能的设备的方式。

HDI印刷电路板:概述在历史上,增加功能性和减小封装尺寸的双重力量共同推动了HDI的发展。为电子产品添加新的特性和功能需要额外的组件和电路,但是市场需求,无论是消费电子产品还是商业电子产品,都需要越来越小的占地面积和更低的功耗(通常以电池寿命来衡量)。HDI首先解决了如何更有效地安装组件的问题。

随着设备之间的距离缩小,工程师们注意到设备间信号的上升时间与整体封装尺寸之间的关系。减小跟踪距离(从一个设备到下一个设备的空间)缩短了设备间电压达到所需水平所需的时间,这既因为距离较低,也因为相应的电容更小。这有助于提高使用开发中的HDI技术设计的产品的性能。

使HDI成为可能的一个关键技术进步是微孔,一种连接电路板上元件的新方法。传统的印刷电路板(PCB)技术,从20世纪40年代末到80年代,依赖于分立元件之间的光蚀刻痕迹,通常使用完全穿过PCB的安装孔(例如使用波峰焊接设备)。从20世纪90年代末开始,微通孔(一种深径比明显低于早期通孔通孔的电路路径)的性能和可靠性受到了严格的测试。当长径比小于1:1时(与长径比在6:1到20:1之间的通孔通孔相比),这些新的、薄的微孔的热循环寿命是以前的许多倍。

最初,他们制造出的微气孔和HDI印刷电路板是基于当时新的表面贴装器件(SMD)技术,即将分立元件焊接到PCB的顶层,而不是穿过多层。然而,随着功能复杂性的不断增长,有必要开发多层安装和设计技术。早期的基准测试表明,与可控阻抗12层通孔设计,8层HDI多层膜将PCB的面积减少了40%,同时也减少了4层。这降低了成本,同时也使更小的产品成为可能。

HDI的好处:左边的绿色PCB是传统的12层通孔控制阻抗设计。黑色PCB显示基准8层HDI重新设计,在相同功能下节省40%的表面积和33%的层深。

多层/微孔法涉及PCB制造过程的所有阶段的变化,尤其是元件和设计:

•组件:组件设计的复杂性持续增加,尺寸不断缩小,这与摩尔定律一致,摩尔定律指出,设备密度大约每19个月翻一番。随着器件密度的增大,对PCB器件的功能要求也随之显著提高。更小的设备可以在一块PCB上安装更多;此外,这些设备通常有更多的连接,这必须在PCB上加以考虑。

•设计:PCB设计,包括刚性和柔性,必须适应表面贴装设备(SMD)结构的连续发展。传统的多氯联苯已经无法满足这些更现代、更复杂的设备的需求。设备有更多的轨迹和更细的间距,需要PCB设计,以解决缩短的距离,以及需要与多层连接的限制,基于SMD的设计。

•制造:正如老派的通孔设计必须逐步淘汰以处理SMD元件,其使用波峰焊接设备的制造工艺也不再适用于现代IC封装。将SMD元件与PCB结合的热黏合剂,取代了传统的从下方焊接引脚的技术。

为什么选择HDI?HDI在性能、封装尺寸和整体重量方面提供了许多优势。当HDI应用于手持、可穿戴和移动电子产品时,这些因素的结合使得HDI尤其具有吸引力。

HDI的主要动机很简单:一个设备中的晶体管数量越多,功能就越强大,性能也就越高。除了在给定产品中使用更强大、更紧凑的设备可以提高性能外,高密度设计的实际几何结构本身也可以提高性能。

较短的记录道(无论是片上记录道还是HDI板上的记录道)减少了电信号在组件之间传输所需的时间。作为另一种电气优势,器件之间的小通孔(特别是当与器件内部的小轨迹耦合时)减小了电路中的总电容,从而减少了信号的上升时间。此外,高密度设计降低了电感,降低了对相邻引线和引脚的影响。这就是HDI在PCB上放置更多晶体管的能力,这不仅使该设备具有更大的功能,而且还带来了更高的性能。

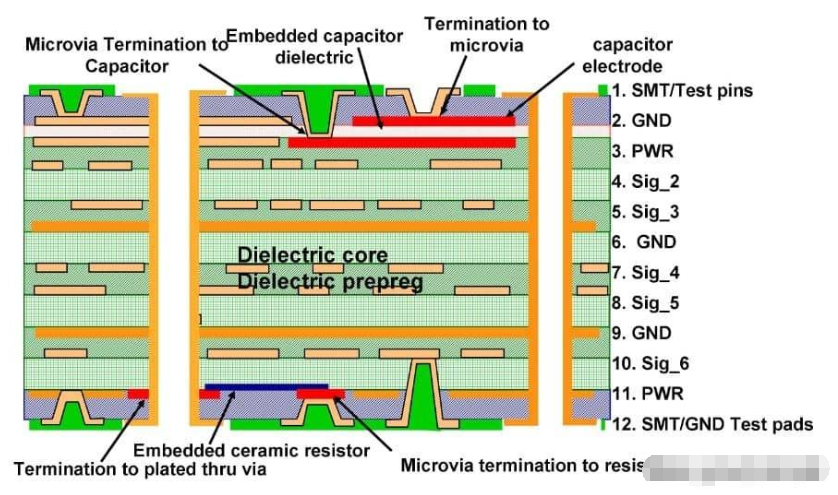

微气孔(红色显示)连接HDI PCB层内的嵌入电容器和电阻。减少导电材料的距离和质量可以提高紧凑、复杂设备的电气性能。

整体电容减少的一个副作用是降低了HDI器件所需的电压。反过来,电压的下降不仅意味着需要更小的电池,而且也减少了热量的产生,这意味着散热问题较少。消除大的散热器硬盘散热和可穿戴电子产品的发展为许多可穿戴电子产品的发展做出了贡献。

最后,以HDI布局和结构为重点的设计和制造过程的开发,减少了原型开发时间和成本,因此可以加快产品引进。这种上市时间(TTM)的缩短意味着更大的盈利潜力,因为潜在客户更快地转化为实际客户。

技术进步使现代HDI成为可能的技术进步本质上是设备制造商和PCB设计者之间的舞蹈,每一个都提供了新的技术,这些新技术要求,或者有时允许另一方随着设备密度的提高而前进。

随着集成电路变得越来越强大和更小,将它们安装到pcb上的技术必须进行调整,以充分利用新的设备。早期的密集型集成电路包括球栅阵列(BGA)器件,在这种器件中,器件的整个下侧都可用于连接,而不是像以前在IC结构中采用标准的双列直插封装(DIP)设计那样在每侧都用引脚封装。BGA支架,其极短的引线,提供了一个重要的步骤,以减少电感相关的信号失真,有助于整体性能的HDI设计。BGA器件的主要负电荷是转换成执行将BGA安装到PCB的机器的初始成本;作为直插式组件主流的波峰焊接机无法满足BGA器件所要求的表面组装。

芯片规模封装(CSP)将BGA原理提升到了一个新的层次。CSP组件最初被称为“芯片尺寸封装”,其设计初衷是器件不会比芯片本身大,器件底部有BGA型引线。这一名称的改变反映了封装的需要,最初的定义是CSP器件的尺寸不超过器件所用芯片的1.2倍。然而,随着半导体制造技术的改进(摩尔定律继续被证明是准确的),芯片本身缩小了,但封装尺寸本身保持不变。CSP的定义改为指安装球间距不超过1mm的设备。

PCB封装的密度有多高?1996年索尼DCR-PC7微型摄像机所用的电路板使用0.15毫米间距的痕迹连接组件两侧的20个CSP设备(0.5毫米间距)。

直接芯片连接(DCA)通过将引线直接沉积在硅上,而不是使用将芯片的焊盘连接到PCB上的痕迹,继续朝着更高密度的方向发展。这种技术有时也被称为“倒装芯片”,因为导电垫安装在晶圆上作为最后的构造阶段,然后器件被倒置安装在PCB上,通常在就位后使用底充工艺覆盖模具的侧面。

从PCB制造商的角度来看,via in-pad design与DCA和CSP合作,以确保这些高密度半导体在最终应用中都到位后有一个高效的工作环境。焊盘内通孔设计将通孔直接置于设备的焊盘下方,这是电感、电容和发热的减少在最终应用中产生差异的地方。电流通孔焊盘设计能够产生间距为0.75mm的迹线,并提供一个平坦的表面,以实现良好的设备连接。

下一步:10nm以下芯片集成电路设计和印刷电路板技术之间的技术飞跃,导致了当今流行的可穿戴和便携式电子设备,从微型数码摄像机和笔记本电脑到智能手机和智能手表。IBM在纽约理工大学的新一代300毫米晶体管设计工厂在纽约理工大学揭幕。虽然10纳米以下的设计已经在实验上进行了十多年的验证,但使用硅锗(SiGe)基片的IBM/SUNY芯片是第一次大规模演示ic生产技术。

这一发展的意义:IBM声称,由于紧密堆叠,这些7nm芯片的表面积比现在的芯片减少了近50%。这一发展的两个关键是使用极紫外(EUV)光进行光刻,以及使用SiGe作为痕迹本身。与目前的光刻标准(波长为193nm的氟化氩激光器)相比,EUV的波长只有13.5nm。此外,标准硅已经无法在7nm处携带足够的电流,因为在如此窄的通道中没有足够的原子来传输信号。锗的加入增加了电子的迁移率,使器件能够正常工作。

7nm芯片距离进入主流制造技术至少还有两年的时间,但用SiGe芯片制造的产品的复杂性和丰富性将是HDI电路设计师的下一个挑战。最初的挑战很可能是设计更小的pcb以适应器件占地面积的显著减少,这很可能需要在小轨迹设计和制造方面取得新的进展。最终,由于设备尺寸的减小总是伴随着性能和复杂度的提高,这些小轨迹设计将被迫以相同或更小的占地面积来应对更大的复杂性和更高数量的互连。HDI的历史表明,这种将IC设计的进步与PCB设计和结构的进步相匹配的平衡行为有望在未来取得令人兴奋的进展。