布线设计是成功的基石:Ansys HFSS引领引线键合仿真潮流

本文原刊登于Ansys Blog:《Wired for Success: Ansys HFSS Leads in Wirebond Simulation》

作者:Kevin Quillen

编辑整理:褚正浩 | Ansys中国高级应用工程师

随着半导体制造商对处理速度的需求日益增长,印刷电路板(PCB)和芯片封装的所有组件都必须以超高的数据速率提供精准的信号完整性。因此,一定要对任何可能导致中断以及信号噪声耦合的设计进行缺陷测试。

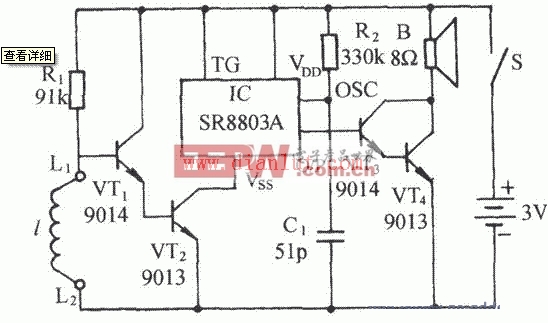

引线键合是在PCB或芯片封装中连接芯片和基板的微小“线路”,其正在接受特别考验。作为连接通道,它们通常是信号损耗或信号退化的根源。半导体工程团队必须将从材料、键合参数到工作环境条件的所有因素纳入考虑,以设计出高可靠性的键合丝。

速度对于分析潜在的键合丝设计以及精准预测其作为PCB或芯片封装一部分的性能至关重要,尤其在进行全面的物理测试所需的预算、员工工时和其它资源都很有限的情况下。那么,电子工程师如何才能在满足严苛发布期限和财务目标的同时,实现提供完美键合丝性能所需的精准分析呢?

无与伦比的性能,充分满足键合丝仿真需求

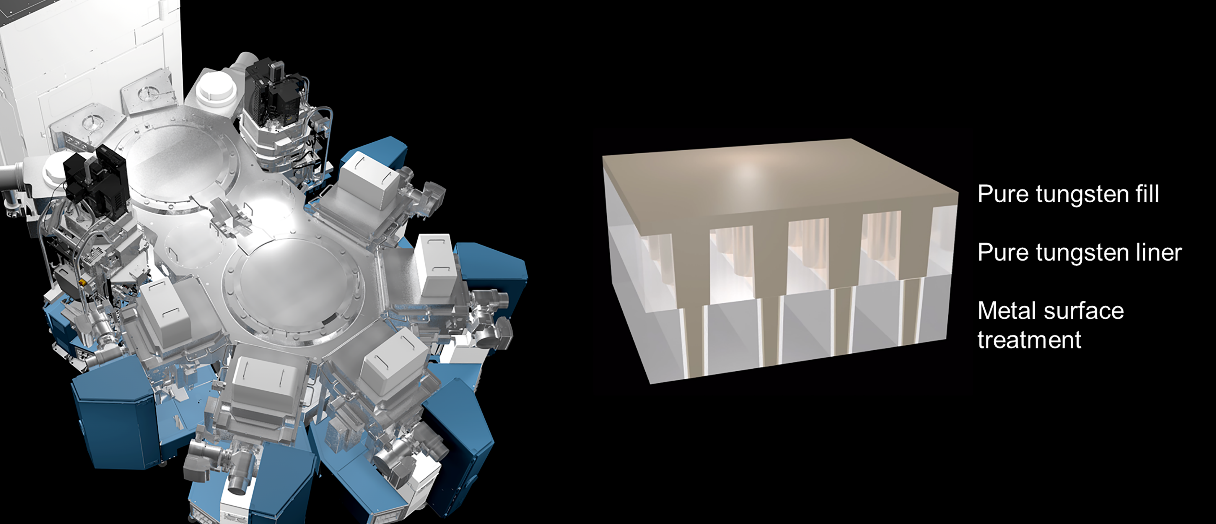

答案是通过Ansys HFSS对键合丝进行建模并仿真其性能,以及所连接的其它方面,包括PCB和芯片封装。

HFSS是仿真高频率信号及电源完整性设计的行业标准,可为绘制、导入和修改键合丝结构提供本地支持。即使面对极高的设计要求,这种高性能的解决方案也能帮助工程师轻松解决诸如材料选择与厚度、封装配置与键合参数等复杂挑战。

在HFSS 3D Layout 2021 R1版本中,Ansys Electronics Desktop又有了更多功能,其中包括强大的全新键合丝编辑平台和数据库管理功能等。工程团队可开发和共享其定制的键合丝配置文件库,因此对于每一款新产品设计无需从头开始。当产品开发商竞相向市场推出新设计时,这不仅可节省时间,而且还可节约成本。

此外,Ansys键合丝库还支持Cadence键合丝设置文件的无缝导入,能够将其存储起来,以备将来使用。

半导体研发的专用端到端解决方案

借助HFSS,工程师不仅可仿真芯片设计,而且还可仿真其在不同使用环境下的信号等级和电源完整性。

在通过HFSS对键合丝进行电气性能优化后,还可采用简单的优化流程,针对热可靠性和结构可靠性等其它物理设计指标对其进行优化。Ansys仿真平台包含HFSS和Ansys Mechanical,可为验证PCB及芯片封装设计(包含键合丝)的电磁、散热和结构等各方面指标提供统一模型的专用环境。

如今更小、更密集的电子封装设计一旦暴露在严酷的现实环境下,发生热故障或结构故障的风险就会更高。作为微小接触点,键合丝必须经过特别严格的故障分析。Ansys仿真技术可轻松并快速地将键合丝设计移交给Mechanical开展此类分析,然后将其返回Ansys HFSS进行迭代设计。

有了HFSS,半导体工程团队不仅可确保针对现实环境优化单个组件,如键合丝等,还可确保整个系统在经过装配、暴露在恶劣工作条件下后,能以可靠的最佳方式协同工作。

全球领先的半导体公司正在运用Ansys解决方案,让其复杂产品的电磁仿真运行实现10-12倍的提速。这种系统级方法,以及针对键合丝优化等特定任务提供的行业领先功能,充分发挥了Ansys 50多年的行业领先地位优势。

随着半导体工程日益复杂,HFSS也在不断发展,以应对各种新的挑战,而HFSS键合丝建模及仿真功能也不例外。Ansys HFSS 2021 R2发布在即,实现更多突破性改进是其不变的承诺,这些改进可预测并满足半导体工程团队最迫切的需求,敬请期待!

关于Ansys CPS 解决方案

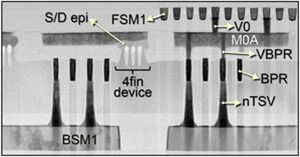

Ansys CPS(Chip+Package+System)多物理场仿真方案,包含了Redhawk/HFSS等业界黄金工具,基于CPM/CSM/CTM等独有的芯片模型,通过协同仿真考察芯片与PKG/PCB之间的耦合影响,通过电、热、结构之间的多物理场耦合仿真使得仿真精度更高,帮助设计者优化从芯片至系统的SIPI/热/结构可靠性等设计指标,此流程已经支持多家客户在先进工艺节点和大规模的2.5D/3D IC设计上成功流片。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。