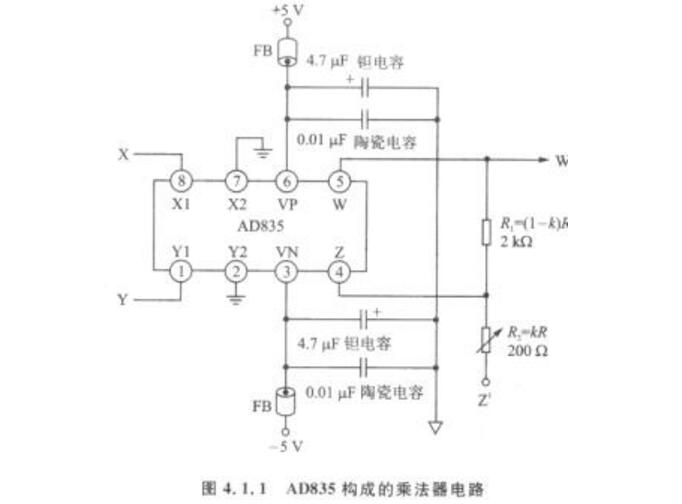

- 在之前的文章中,我们了解了同步解调技术的基础知识。该技术有助于测量隐藏在闪烁噪声中的低频信号。它试图以比电路的 1/f 拐角频率高得多的频率运行电路,以便闪烁噪声不再是限制因素。在之前的文章中,我们了解了同步解调技术的基础知识。该技术有助于测量隐藏在闪烁噪声中的低频信号。它试图以比电路的 1/f 拐角频率高得多的频率运行电路,以便闪烁噪声不再是限制因素。同步解调技术可以使用模拟乘法器或基于开关的乘法器来实现。从实现的角度来看,基于开关的乘法更方便。在本文中,我们将探讨使用此类乘法器的优缺点。使用模拟乘法器

- 关键字:

乘法器

- 何 进,衣溪琳,张子骥,贺雅娟(电子科技大学 电子科学与工程学院,四川 成都 610054) 摘 要:本文提出一种可靠的低功耗近似乘法器设计方案,该方案基于嵌入式算法容噪技术,并且通过阈值的合理选择简化了传统嵌入式容噪方案中的检错纠错模块。我们根据这样的思路基于SMIC 180 nm工艺设计了相应的8比特乘8比特的近似乘法器。该乘法器在450 MHz的工作频率最低可以工作在1.2 V的电源电压下。与传统的阵列乘法器相比,在相同的工作频率和MSE条件下,传统乘法器可以工作在1.6 V左右,该乘法器可以

- 关键字:

201908 低功耗 低压 乘法器 算法容噪技术 阈值选择

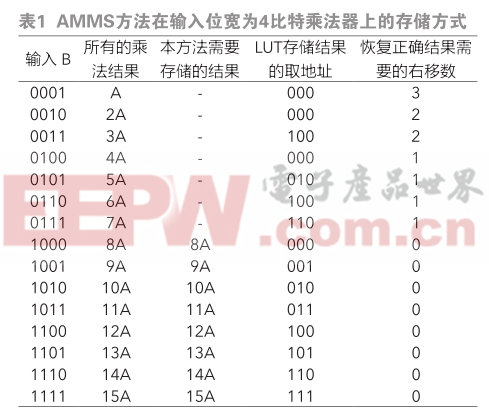

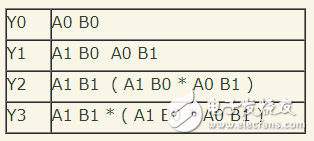

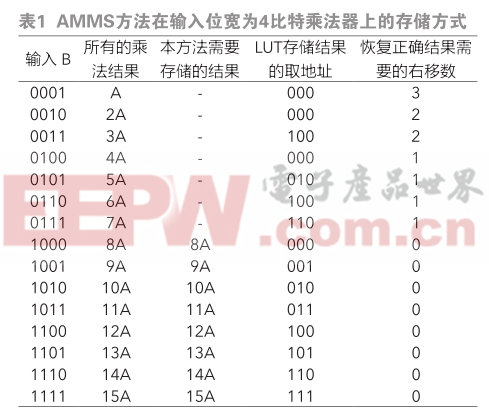

- 万晨雨,贺雅娟 (电子科技大学电子科学与工程学院,成都 610054) 摘要:本文提出了一种近似高输入结果存储(approximate-most-significant-multiple-storage, AMMS)的查找表(LUT)优化方法。该方法利用移位操作来替代部分存储,并将存储内容进行截位使存储位宽缩减,对基于存储的乘法器中的查找表进行了优化。该方法在一个mm位的乘法器中,可以将查找表的规模缩减至传统存储方法的1/4,并明显改善乘法器的面积延迟积(ADP),不过与此同时,该方法也因截位而产

- 关键字:

201907 存储 乘法器 优化

- 过去的40年中,MOS器件尺寸的持续缩小一直是促进半导体工业发展的动力。人们可以在越来越小的芯片上实现越来越复杂的功能,并且芯片的价格不断下降,使得各种便携式产品如笔记本电脑、笔迹识别仪。

- 关键字:

绝热逻辑 低功耗 乘法器

- 如前所述,本系统主要完成对输入视频图像的两倍放大。图像的放大主要是通过插值算法来实现的,下面详细分析如何应用双线性插值算法来实现倍焦功能。

- 关键字:

数字图像倍焦系统 乘法器 FPGA

- 采用乘法器的可变环宽比较器电路图图采用乘法器的可变环宽比较器电路图

- 关键字:

乘法器 可变环宽 比较器

- 为什么不能将乘法器用作调制器或混频器?它们不是一回事吗?并非如此,了解它们之间的区别十分重要。乘法器有两个模拟输入,输出与两个输入幅度的乘积成比例。VOUT = K times; VIN1 times; VIN2其中,K是维数为1/V的

- 关键字:

乘法器 调制器 混频器

- 高端设计工具为少有甚是没有硬件设计技术的工程师和科学家提供现场可编程门阵列(FPGA)。无论你使用图形化设计程序,ANSI C语言还是VHDL语言,如此复杂的合成工艺会不禁让人去想FPGA真实的运作情况。在这个芯片中的

- 关键字:

FPGA 乘法器 触发器 DSP RAM

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

调制器 乘法器 信号频带 谐波 基波

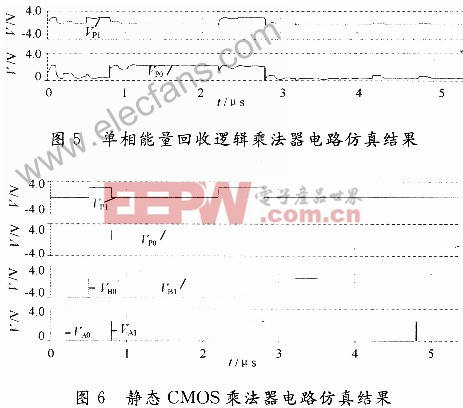

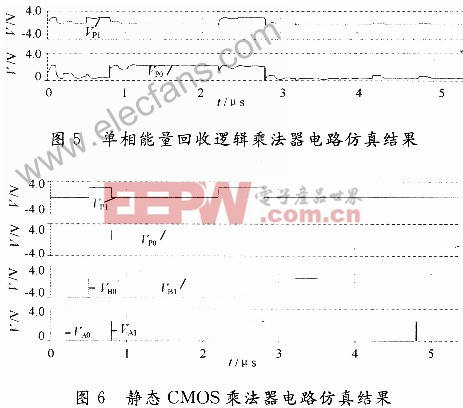

- O 引言 电路中的功率消耗源主要有以下几种:由逻辑转换引起的逻辑门对负载电容充、放电引起的功率消耗;由逻辑门中瞬时短路电流引起的功率消耗;由器件的漏电流引起的消耗,并且每引进一次新的制造技术会导致漏电流

- 关键字:

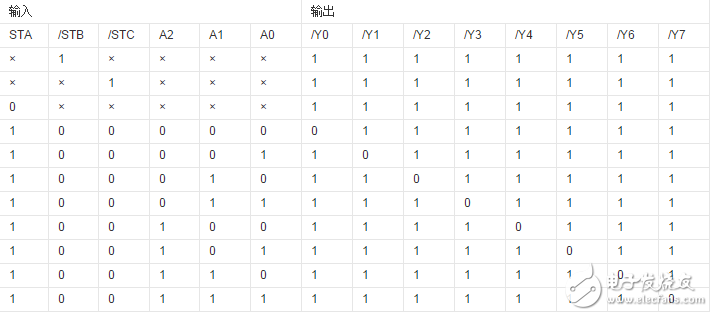

CMOS 单相 乘法器 能量回收

- 摘要:设计了一款嵌入FPGA的乘法器,该乘法器能够满足两个18 b有符号或17 b无符号数的乘法运算。该设计基于改进的布斯算法,提出了一种新的布斯译码和部分积结构,并对9-2压缩树和超前进位加法器进行了优化。该乘法器

- 关键字:

FPGA 算法 嵌入式 乘法器

- 脉冲-宽度-高度调制乘法器双称为时间分割乘法器。这类乘法器电路原理图如图5.4-24A所示。图中,三角波电压UT和模拟输入电压UY相加,然后通过零电平比较器,得到不对称方波控制电压U2。U2的工作周期取决于UY的大小和极

- 关键字:

脉冲 调制 乘法器 分析

- 除了瞬时功率外,平均和RMS功率值也是非常重要的。所有全模拟电路可以实现这些指标的测量。对于电机或伺服器这些需要精确监视或调节负载耗散功率的产品来说,可以通过计算负载电压和电流的乘积来测量实际功率。但如果

- 关键字:

PWM 测量 高频 乘法器

- 本文提出了一种高频四象限电流乘法器。该乘法器电路结构对称。提出的乘法器电路工作在±1.18 V的电源电压下 ...

- 关键字:

高频 四象 限电流 乘法器

乘法器介绍

乘法器

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘。它是由更基本的加法器组成的。

目录

1简介

2作用

3类型

·模拟乘法器

·硬件乘法器

1简介

乘法器(multiplier)可以通过使用一系列计算机算数技术来实现。大多数的技术涉及了对部分积(partial product) [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473