- 西门子数字化工业软件近日推出 Tessent™ RTL Pro 创新软件解决方案,旨在帮助集成电路 (IC) 设计团队简化和加速下一代设计的关键可测试性设计 (DFT) 任务。随着 IC 设计规模不断增大、复杂性持续增长,工程师需要在设计早期阶段发现并解决可测试性问题,西门子的 Tessent 软件可以在设计流程早期阶段分析和插入大多数 DFT 逻辑,执行快速综合,运行 ATPG(自动测试向量生成),以发现和解决异常模块并采取适当的措施,满足客户不断增长的需求。Tessent RTL Pro 进一步扩展了

- 关键字:

西门子 Tessent RTL Pro 可测试性设计

- · 将 RTL 收敛速度加快 5 倍,结果质量改善 25%· RTL 设计师可快速准确地了解物理实现指标,根据提供的指引有效提升 RTL 性能· 与 Cadence Cerebrus 和 Cadence JedAI Platform 集成,实现 AI 驱动的 RTL 优化中国上海,2023 年 7 月 17 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布推出 Cadence® Joules™ RTL

- 关键字:

Cadence RTL

- 楷登电子(美国Cadence公司)今日正式发布JasperGold® 形式验证平台扩展版,引入高级形式化验证技术的JasperGold Superlint和Clock Domain Crossing (CDC)应用,以满足JasperGold形式验证技术在RTL设计领域的签核要求。较现有验证解决方案,Superlint和CDC应用提高了IP设计质量,后期RTL变更最高减少80%, IP开发时间缩短4周。如需了解更多关于JasperGold技术

- 关键字:

Cadence RTL

- EDA 公司和 FPGA 厂商不断开发新的工具和方法,推进繁琐任务的自动化,帮助设计团队集中精力做好创造性工作。下面我们就来看看 FPGA 工具流程的演进发展,了解一下现代 FPGA 团队是如何利用 RTL分析、约束生成和综合导向来减少设计迭代的。

- 关键字:

RTL SDC 综合向导 FPGA

- Mentor Graphics 公司今天发布了最新版的 Catapult® 平台。与传统手工编码的寄存器传输级 (RTL) 相比,该平台将硬件设计的时间从设计启动到 RTL 验证收敛缩短了 50%。虽然现有的高级综合 (HLS) 方法可将设计和验证生产率提高多达 10 倍,但是完成最终 RTL 验证所需的时间还是可能会抵消这些优势。而此次发布的 Catapult 平台结合 HLS 与成熟可靠的验证方法以及新工具,其中,新工具能够在 C++/SystemC 级验证收敛(实现 C++/SystemC si

- 关键字:

Mentor RTL

- 这次我们讲一讲如何入门学习硬件描述语言和数字逻辑电路;学习数字逻辑电路,我推荐的一本书就是--《数字设计-原理与实践》,其他的深入点可以看看《完整数字设计》;而对于硬件描述语言呢?有两个原则,一个是买书的原则,一个是看书的原则。首先,你必须买两类书,一类是语法书,平常使用的时候可以查一查某些语法;一类是,对语言的使用的讲解和使用的方法(如何书写RTL,如何设计电路,如何调试代码,使用仿真器等);我用过一年的VHDL和两年的Verilog;作为过来人,我想介绍一些比较好的书给入门者,避免大家走弯路。

- 关键字:

Verilog RTL

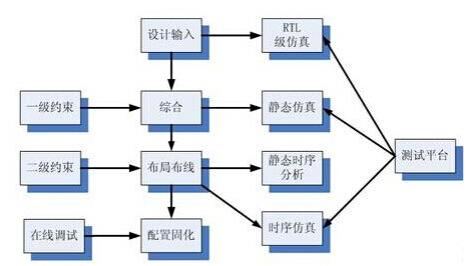

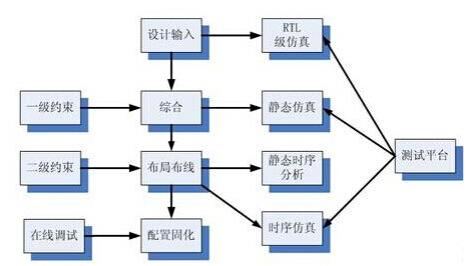

- 要知道,要把一件事情做好,不管是做哪们技术还是办什么手续,明白这个事情的流程非常关键,它决定了这件事情的顺利进行与否。同样,我们学习FPGA开发数字系统这个技术,先撇开使用这个技术的基础编程语言的具体语法、使用工具和使用技巧不谈,咱先来弄清楚FPGA的开发流程是什么。

FPGA的开发流程是遵循着ASIC的开发流程发展的,发展到目前为止,FPGA的开发流程总体按照图1进行,有些步骤可能由于其在当前项目中的条件的宽度的允许,可以免去,比如静态仿真过程,这样来达到项目时间上的优势。但是,大部分的流程步

- 关键字:

FPGA RTL

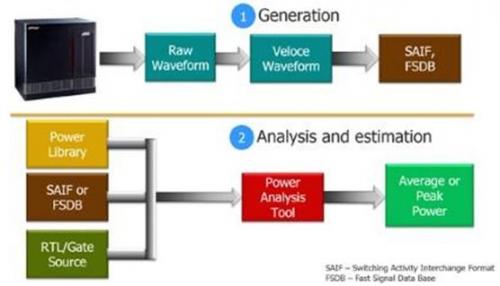

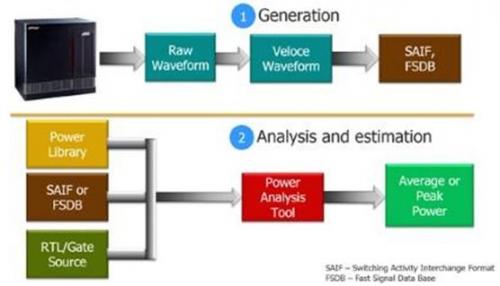

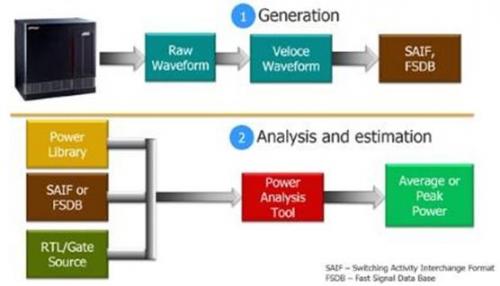

- 通过省去基于文件的流程,新工具可提供完整的 RTL 功率探测和精确的门级功率分析流程。

在最近发布的一篇文章中,笔者强调了当前动态功耗估算方法的内在局限性。简单来说,当前的方法是一个基于文件的流程,其中包括两个步骤。第一步,软件模拟器或硬件仿真器会在一个交换格式 (SAIF) 文件中跟踪并累积整个运行过程中的翻转活动,或在快速信号数据库 (FSDB) 文件中按周期记录每个信号的翻转活动。第二步,使用一个馈入 SAIF 文件的功率估算工具计算整个电路的平均功耗,或使用 FSDB 文件计算设计时间和

- 关键字:

SoC RTL

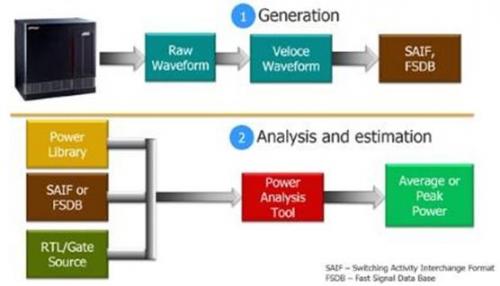

- 通过省去基于文件的流程,新工具可提供完整的 RTL 功率探测和精确的门级功率分析流程。

在最近发布的一篇文章中,笔者强调了当前动态功耗估算方法的内在局限性。简单来说,当前的方法是一个基于文件的流程,其中包括两个步骤。第一步,软件模拟器或硬件仿真器会在一个交换格式 (SAIF) 文件中跟踪并累积整个运行过程中的翻转活动,或在快速信号数据库 (FSDB) 文件中按周期记录每个信号的翻转活动。第二步,使用一个馈入 SAIF 文件的功率估算工具计算整个电路的平均功耗,或使用 FSDB 文件计算设计时间和

- 关键字:

SoC RTL

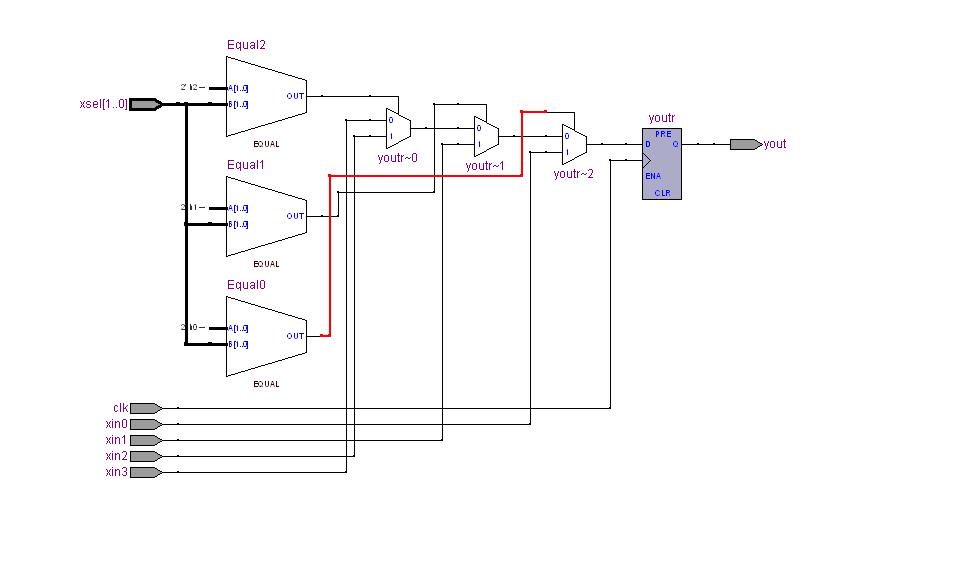

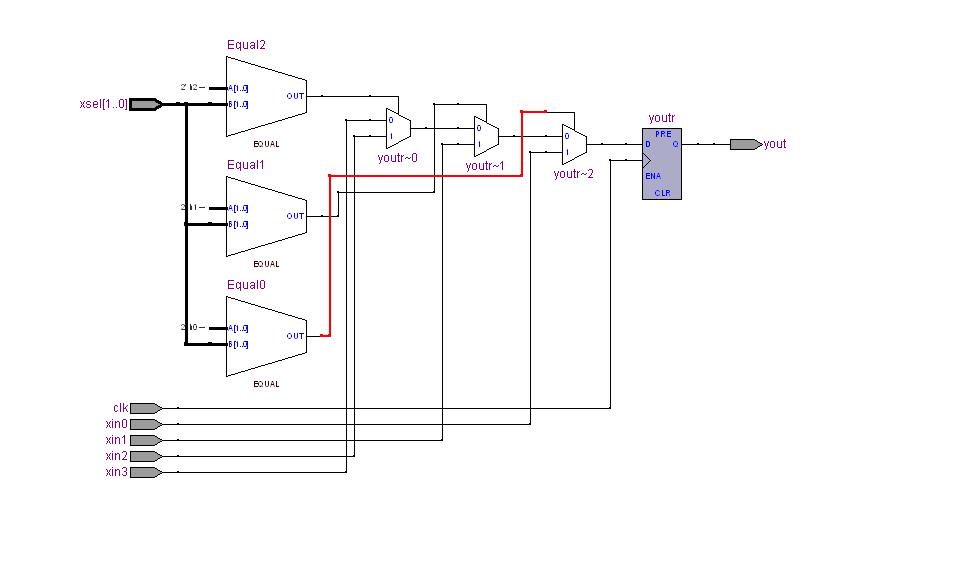

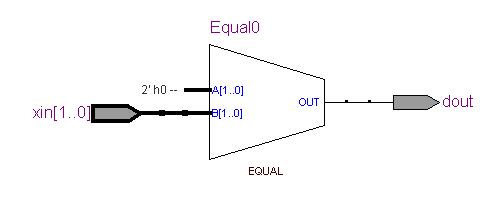

- 我们来做一个4选一的Mux的实验,首先是利用if…else语句来做,如下。

(由输入xsel来选择输出的路数xin0,xin1,xin2,xin3其一,输出yout)

Ex3:

input clk;

input xin0,xin1,xin2,xin3;

input[1:0] xsel;

output yout;

reg youtr;

always @ (posedge clk)

if(xsel == 2'b00) youtr <

- 关键字:

verilog RTL

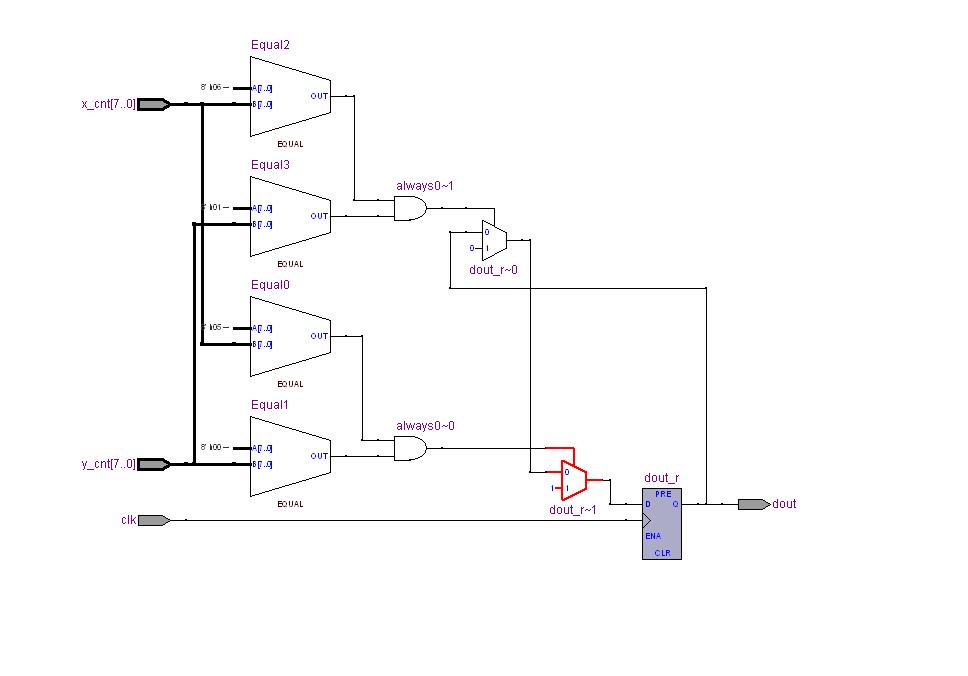

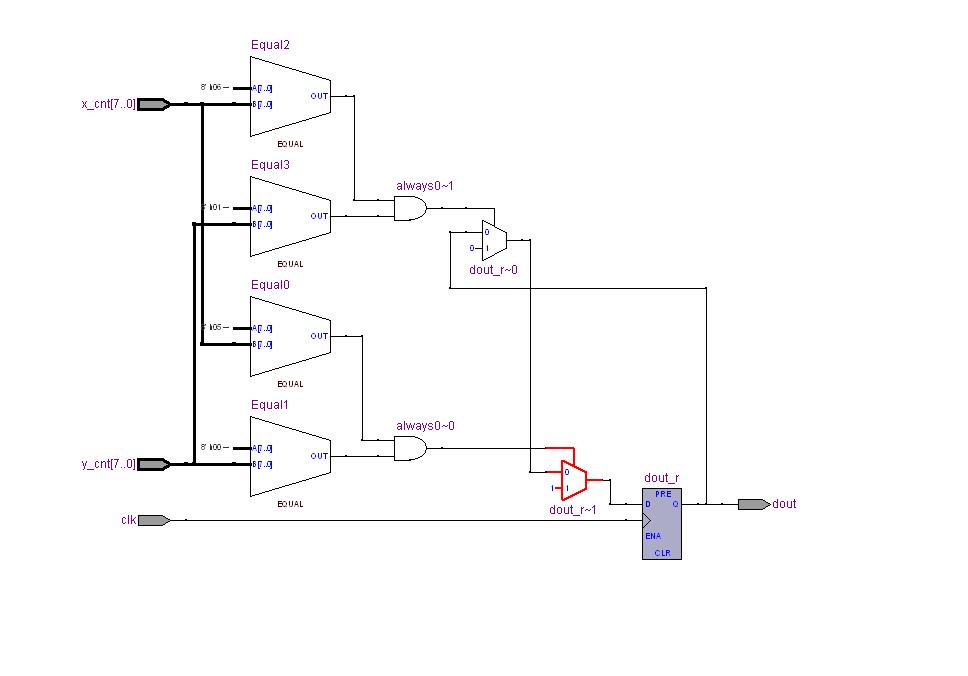

- 这次要说明的一个问题是我在做一个480*320液晶驱动的过程中遇到的,先看一个简单的对比,然后再讨论不迟。

这个程序是在我的液晶驱动设计中提取出来的。假设是x_cnt不断的增加,8bit的x_cnt加一个周期回到0后,y_cnt加1,如此循环,本意是要让下面的dout信号只有在x_cnt>=5 & y_cnt=0或者x_cnt<= 4,y_cnt=1这个区间内为1,其它时刻内为0。一般而言会有如下两种描述,前者是时序逻辑,后者是组合逻辑。当然除了下面两种编码风格外,还可以有很

- 关键字:

verilog RTL

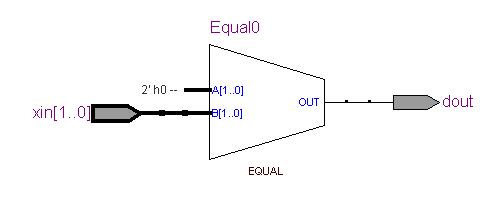

- 刚开始玩CPLD/FPGA开发板的时候使用的一块基于EPM240T100的板子,alter的这块芯片虽说功耗小体积小,但是资源还是很小的,你写点稍微复杂的程序,如果不注意coding style,很容易就溢出了。当时做一个三位数的解码基本就让我苦死了,对coding style的重要性也算是有一个比较深刻的认识了。

后来因为一直在玩xilinx的spartan3 xc3s400,这块芯片资源相当丰富,甚至于我在它里面缓存了一帧640*480*3/8BYTE的数据都没有问题(VGA显示用)。而最近

- 关键字:

FPGA verilog RTL

- 我接触逻辑设计有三年多的时间了,说是三年,其实真正有大的提高就是在公司实习的那一年期间。在即将去公司报到之前,把一些东西写下来,希望让大家少走些弯路。

学习逻辑设计首先要有项目挂靠,如果你觉得未来一段时间你都不可能有的话,接下来的内容你就没有必要再看了,花的时间再多也只能学到皮毛--很多细节的问题光写代码是发现不到的。而且要真正入门,最好要多做几个项目(这三年大大小小的项目我做有七八个),总线型的和数字信号处理型的最好都要接触一些,因为这两个方向的逻辑设计差异比较大:前者主要是控制型的,会涉及到

- 关键字:

逻辑设计 IC RTL

- 在项目设计初期,基于硬件电源模块的设计考虑,对FPGA设计中的功耗估计是必不可少的。笔者经历过一个项目,整个系统的功耗达到了100w,而单片FPGA的功耗估计得到为20w左右,有点过高了,功耗过高则会造成发热量增大,温度高最常见的问题就是系统重启,另外对FPGA内部的时序也不利,导致可靠性下降。其它硬件电路的功耗是固定的,只有FPGA的功耗有优化的余地,因此硬件团队则极力要求笔者所在的FPGA团队尽量多做些低功耗设计。笔者项目经历尚浅,还是第一次正视功耗这码事儿,由于项目时间比较紧,而且xilinx方

- 关键字:

FPGA 低功耗 RTL

- Excellicon公司,一家时序约束分析和调试解决方案的供应商,可以提供自动化的时序约束编辑、编译、管理、实现和验证,日前宣布其产品被灿芯半导体采用,灿芯半导体是一家背靠中芯国际集成电路制造有限公司的设计服务公司,提供复杂的SOC和ASIC设计服务。 Excellicon工具很好的帮助灿芯半导体生成灵活的、客制化的、符合成本效益的设计流程,以便缩短复杂芯片的设计开发时间,该工具可以满足复杂的时序约束开发、验证和管理需求。Excellicon工具有望加快时序收敛过程并消除设计和实现工程之间无数次迭代

- 关键字:

Excellicon 灿芯 RTL

rtl-to-gdsii介绍

您好,目前还没有人创建词条rtl-to-gdsii!

欢迎您创建该词条,阐述对rtl-to-gdsii的理解,并与今后在此搜索rtl-to-gdsii的朋友们分享。

创建词条

- 如何读懂数字电路RTL设计?

- 深圳IC厂商诚聘资深数字IC设计工程师

- 紧急求助.求一个版图数据格式CIF格式转GDSII格式的小软件

- 紧急求助.求一个版图数据格式CIF格式转GDSII格式的小软件

- KEIL,RTL,HTTP,DEMO,EASYARM2200,nbsp,nbsp,WEB KEIL-RTL HTTP-DEMO EASYARM2200

- MSP430,RTL8019 MSP430+RTL8019(新手上路,多多指教)

- Keil,ARM,RV,RTL,KIT 急切寻找 Keil ARM RV-RTL KIT ???

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473