IGLOO─业界极低功耗的FPGA

随着半导体工艺的飞速发展和芯片工作频率的提高,芯片的功耗迅速增加,而功耗增加又将导致芯片发热量的增大和可靠性的下降。因此,功耗已经成为深亚微米集成电路设计中需要考虑的一个重要因素。为了使产品更具竞争力,工业界对芯片设计的要求已从单纯追求高性能、小面积转为对性能、面积、功耗的综合要求。

本文引用地址:https://www.eepw.com.cn/article/92555.htm芯片对功耗的苛刻要求源于产品对功耗的要求,由于集成电路的迅速发展和对消费类电子产品,特别是便携式(移动)电子产品的需求日新月异,使得设计者对电池供电的系统已不能只考虑它优化的两个方面——速度和面积,而必须要注意它已经表现出来的且变得越来越重要的第三个方面─功耗,这样才能延长电池的寿命和电子产品的运行时间。

本文主要介绍基于FPGA功耗的相关知识,例如功耗的分类、功耗的组成、如何降低功耗以及选择一个合适的低功耗器件等,让读者对FPGA的功耗具有感性的认识。

1.FPGA功耗的基本概念

(1) 功耗的组成

无论是FPGA还是MCU,功耗的一般都是由两部分组成:静态功耗和动态功耗,静态功耗主要是由晶体管的漏电流引起,由源极到漏极的漏电流以及栅极到衬底的漏电流组成;动态功耗主要由电容充放电引起,其主要的影响参数是电压、节点电容和工作频率,可以用公式(1)表示。

P=α×CL×V2dd×f (1)

(2) 静态功耗

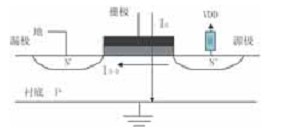

静态功耗主要是由漏电流引起,漏电流是在芯片上电的时候,无论是处于工作还是处于静止状态,都一直会存在的一个电流,来源于晶体管的三个极,如图1所示,它分为两部分,一部分是来自源极到漏极的泄漏电流IS-D,另一部分是来自栅极到衬底的泄漏电流IG,漏电流与晶体管的沟道长度和栅氧化物的厚度成反比。

源极到漏极的泄漏电流IS-D:也称为亚阀值电流,是泄漏的主要原因,我们都知道MOS管在关断的时候,沟道阻抗非常大,但是再大都会有一个值,所以只要芯片供电必然会存在一个从源极到漏极的泄漏电流,随着半导体工艺不断先进,晶体管尺寸不断减小,沟道长度也逐渐减小,使得沟道阻抗变小,从而IS-D变得越来越大,而且源极到漏极的漏电流随温度增加呈指数增长,例如:结温从25℃上升到85℃时源极到漏极的泄漏电流会增加5倍之多。

栅极到衬底的泄漏电流IG:虽然没有亚阀电流那么关键,但是也非常重要,栅极的漏电流随着栅氧化物的厚度减小而增大,特别在65nm、45nm的技术中显得尤为突出。

图1 漏电流示意图

评论