低功耗嵌入式实现的方方面面

任何一个嵌入式设计都是在对电源供电结构进行详尽分析后才能完成的;同样,对于恒定电源供电的有线系统也是如此。处理器和其周边的硬件生态系统的消耗通常占电源的较大比例,因此,这就是所有的“重点”之所在。

本文引用地址:https://www.eepw.com.cn/article/91242.htm在深入讨论之前,我们先按次序讨论一下术语。“能量”与做功的总量有关,而“功率”是测量做功的速率(单位时间的能量)。电子学中,功耗= (系统元器件的电压)ⅹ(流经系统元器件的电流),能量=功率ⅹ时间。

因此,系统设计员通常关心总的能量消耗和峰值功耗。换句话说,使用的能量是从电池吸收的,但电池也需要提供足够的瞬时能量以满足峰值功率的要求。习惯上将集中讨论功耗;然而,实际上也将论及系统中使用的能量和功率。

什么是“低功耗”

“低功耗”究竟指什么?从嵌入式观点看,经常将该术语同电池驱动移动设备联系起来,但该术语实质上也是相对的。从功率尺度的最低端应用看,我们可以只简单地讨论手表电池的例子。然而,在另一个极端,为了避免额外的设计负担和费用(如热同步、风扇、调整器等),又需要构想使功耗最小的“插入式”系统。

毕竟现今的很多设计系统,诸如从汽车收音机到“插件箱”中的仪器板卡,都是根据交到OEM(原设备供应商)的规格构建的系统。为了确保销售商之间的一致,这些规格经常描述了严格的功率预算分配。关键点是,为了关注降低功耗,系统不一定非要用电池供电,或者非要“移动”。

为了方便,可以将低功耗嵌入式系统分为三个不同类型:

第一类是在不使用时就关闭电源的系统。对于这类应用,系统运行时的低电流消耗驾驭着电池的寿命。这样的应用实例包括便携式媒体播放器、GPS设备和数码相机,这些系统在工作状态呈现出低功耗的特性,同时待机电流是“无关紧要”的,这是由于设备关闭时是不吸收电流的(如果使用了实时时钟会有几微安的电流)。通常根据不同的应用,处理器在有效工作状态时的电流从几十到几百毫安。

第二类中,将开机或完全关闭的系统改进为开机或“待机模式”的系统。在待机状态,系统处于最低电流消耗状态,同时仍维持存储区中的内容。对于这样的系统,有效电流和待机电流消耗都很重要,此时有效电流的消耗与第一种情况相同,而待机电流通常则从数百微安到几毫安。这种类型的典型产品如VoIP移动电话和声控设备。该类还包括这样的情况,系统的某部分仍处于“监控”状态,在转换到全速处理状态之前等待某事件的发生。

第三类由始终处于加电状态的设备构成。这里,功率要求很可能在次毫安范围内,这就直接限制了可实现的处理性能。此类的应用实例包括手表和一些便携式或植入式医疗设备。

有很多方法可以调整系统的功耗指标,以满足应用要求,包括:

·动态改变频率和电压;

·了解处理器内分离的供电范围;

·分析代码从而针对降低功耗做优化;

·运用处理器的多种供电模式;

·从系统级关注功耗的产生。

本文将集中讨论最后两种方法,参考文献部分列出了其他几个主题的详细说明。

电源供电模式

许多应用涉及相对于其处理的需求有明显差别的工作模式。考虑一个用电池供电并带有嵌入处理器的传感器。处理器的外设可能采集周围环境的参数。在该模式下,不要求有计算功率,处理器可能要求突发读入遥测数据的数据包。当处理器读取足够数据并开始处理时,则进入“全速”工作模式,整个处理器就被唤醒,以最高的性能运行。当不需要传感器数据也不需要处理时,可提供超低功耗模式。

处理器要从各种各样的掉电模式中唤醒,需要接收某种类型的唤醒事件。外部事件可以是外部激励,如标志引脚翻转,或者内部处理器活动,如DMA传输完成或定时器满等。

不同处理器上实现的确定电源供电模式有很大差别,但处理平台之间通常也有一些共性,例如“全速”工作模式;“睡眠”模式,为了使系统快速恢复,即使处理器未使用的部分为省电处于无效,片上存储器仍保持供电;以及“休眠”模式,此模式中,为了最大节省电源,片上存储器也可以不供电。本文中,“待机模式”表示综合的低功耗模式,这里的电流消耗和恢复到全速处理模式所需的时间需要进行折中[v1],也就是电流越低,恢复到全速工作的时间就越长。

为什么需要让处理器定期进入或退出待机模式呢?其实很简单,就是为了减少能量消耗和延长电池寿命。在许多待机模式中,由于处理器仍然被供电,处理器可保留其所有的内部状态和存储器内容,但大大地减少了电流的吸收。此外,处理器唤醒需要占用几毫秒时间,但这也比传统的处理器从冷启动加载快得多。

休眠模式

“休眠”待机模式是特别有意思的,因为它通过完全关闭处理器内核电源,实现了最大的能量节省 (与“待机综合”下的其他模式不同)。 当处理器内核的电源关闭后,不再维护处理器的内部状态,因此,任何保存在内部(存储器内容、寄存器内容等)的关键信息,在关电前都必须提前写入到非易失性存储器设备中。然而,即使关闭了处理器内核电源,休眠方式仍为使SDRAM保持“活跃”状态提供了措施。在进入休眠模式前,设置SDRAM进入自刷新模式,并在唤醒后可以重新控制它,处理器允许将系统状态存储在易失性DRAM中,而不是非易失性Flash存储器中,这样,处理器在唤醒后就可以更快速自举,否则,处理器还需要从非易失性存储器重新载入程序代码。

充分利用电源供电模式

现在考虑另一个具有代表性的情况,此时有不同的处理器供电模式,在功耗方面也有很大的差别。考虑一台带有输入缓冲区的便携式MP3播放器,将音频数据解码到SDRAM中的输出缓冲区,然后将处理器置为待机模式,直到又需要新的数据为止。

由于MP3解码处理要求低,在不需要处理的间隔,处理器可以进入休眠状态,比如,设备可能工作在“25%解码,75%休眠”的情形,也就是说,此时处理器在这个25%的时间时,其内核吸收电流是30mA,而在75%的时间时,处理器内核的吸收电流仅有15mA。在解码间隔,处理器尽可能快的在外部存储器中构建解码的样本,一旦达到了缓冲区期望的大小,处理器就进入睡眠状态,直到需要更新数据缓冲区。

换句话说,如果通常进行连续流MP3解码,即75MHz,则可选择以300MHz对在待机模式过程中收集的缓冲区数进行解码。这样,处理器就在一个更高水平上运行,但其运行过程很短(在处理器又回到睡眠状态前)。通过使睡眠时间最大化,就可以节省能量。这种方法只是对于像便携式媒体播放器这样的系统是有道理的,因为有时也需要视频处理,否则,如果只是MP3解码,就可使用更低性能(和低功耗)的处理器。

那如何管理处理器的唤醒速率呢?在本例中,音频缓冲可以是双缓冲,从DMA角度看,每个缓冲区就是一个音频“线”,每个输出线完成的中断就标志处理器是时候用新数据填充刚为空的缓冲区了。在输出缓冲区准备通过音频口进行播放之前,处理器很容易产生所需要的解码后的输出缓冲区数据,一旦处理器填满了该缓冲区,它又进入睡眠状态,然后不断重复这一过程。

作为旁注,在上述例子,使用异步SRAM设备而不是SDRAM,更能节省成本和节省能量。当然,SRAM不能提供和SDRAM一样的性能水平,但对于16bit或32bit访问的音频数据, SRAM的性能就足够了,这是因为采用DMA控制器并行访问数据,即使数据以低速SRAM速率出现,也很容易保持持续给串行接口提供解码数据。

由于有较大的程序代码,或者需要提高解码的性能,即使应用中需要SDRAM,在设计中同时使用SRAM和SDRAM也是有道理的。当然使用的材料成本费用将增加,在系统中巧妙地使用两者也可以最大化地节省功率。要求最高性能的部分应用可使用SDRAM,且每当处理器进入睡眠后,即将SDRAM置为自刷新模式。在活跃处理期间,吸收的电流主要由处理器和SDRAM控制,这是因为基于mW/bit SRAM虽然不如SDRAM有效,但其尺寸大小通常比SDRAM小的多。

在低功耗应用中优化功率消耗

利用系统级技术节省功耗与元器件级节省同样重要,因为元器件经常以共生的形式一起使用。当将处理器置为低功耗模式,许多不同的系统元器件都可以配置为用于唤醒处理器,比如,通过以太网、USB、实时时钟或FLAG标志引脚上的触发信号等都可以产生唤醒事件。

一个较好的系统级唤醒实例是通过串行口连接到处理器的外部WiFi芯片。 当处理器没有活跃地运行时,可以将它置入低功耗状态,仅让WiFi芯片运转。在这种工作状态,WiFi芯片中的微控制器几乎不消耗电流,因为它仅仅查找与分配的MAC地址相关的数据包,一旦接收数据包,WiFi芯片就向处理器发送一个信号,唤醒处理器并开始再工作。

实时时钟

如果便携式系统还承担着维护日历时间的任务,此时可用实时时钟(RTC),从应用观点(例如,将实际日期和时刻传递给用户)和功耗的观点看,这都很重要。多数RTC都允许设置闹钟,在未来任何时间点提供唤醒功能。 因此,系统在不活跃的周期可转入到待机模式,在监视、管理或者用户通知任务等周期性间隔即可唤醒系统。

作为低功率系统中RTC是如何用的一个具体实例,让我们假设对于GPS应用,需要每秒唤醒处理器获得卫星的位置,RTC(吸收20μA)设置为每秒唤醒处理器,处理器转入其低功耗模式(消耗50μA)。当RTC闹钟响起时,处理器被唤醒,执行算法,获取卫星座标,然后再回到睡眠状态。因此,在这种应用中,仅有很低的“在线”占空比,主要工作时间仅需消耗70μA的电流。

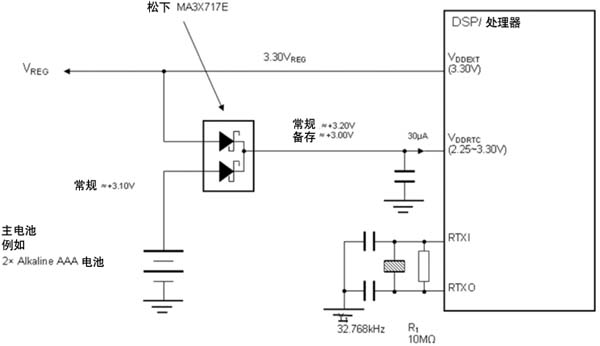

无论是作为处理器的一部分,或作为连接到处理器的一个独立芯片,RTC都需要一个独立的电源域,当系统其他部分的电源关闭后它仍可以保持工作。RTC通常采用硬币大小的微型电池供电工作,仅消耗微瓦级能量。由于扩展电池寿命十分重要,当系统连接使用了主电源,允许系统通过主电池(或线路电源)为RTC提供电源运行是明智的。当系统其他部分供电运行时,图1说明了可用于节省RTC电池吸收电流的电路实例。

图 1 RTC的主微型电池备用供给

输入时钟

处理器的输入时钟引脚提供必要的时钟频率、占空比和稳定性,通过片上锁相环(PLL)模块倍乘后,可产生精确的内部时钟。时钟引脚连接外部晶体或晶体振荡器,使用晶体通常很便宜,但使用的晶振通常进行了缓冲,还可以为系统中的其他部分提供可选的时钟使用。例如,27MHz的晶振不仅可作为处理器时钟输入,还可以作为NTSC视频编码器或译码器的时钟源。有时,处理器本身也基于晶体输入时钟,提供缓冲的时钟输出,这就可节省购买晶振的费用。

基本振荡频率越低,晶体的封装就越大,然而,更高频率的晶体成本又高,因为它们更易碎。因为基频越高,里面的石英就越薄。权衡是否使用晶体的另一个因素还有EM(电磁干扰)。要控制晶体可能泄漏到滤波器或者运放通带内的寄生谐波,从系统角度看避免某个频率倍数也是十分重要的。

在某些处理器中,当处理器进入低功耗模式时,可编程停止输入晶振放大器驱动,这可节省几个mA的吸收电流,而这样做的开销来自于当处理器恢复正常活动时,会增加开机时间(由于时钟设置延迟)。

USB

如今许多便携式设备都有USB连接方式,USB除了作为普遍使用的到PC机的连接方式外,它也为设备提供了一种公共的供电源。当设备连接到PC机时,它可使用主机作为源对其供电,这对于节省电池寿命有实际效果,同时也为嵌入式产品中的电池充电提供了一种方法。

USB供电的设备的供电属性必须符合USB规范的预算,USB 1.1和USB 2.0协议限制每个设备的“总线供应”功率为2.5W(0.5A @ +5V),对于低功率设备如键盘或鼠标是足够的。

USB标准也定义了支持更高电流的设备,但总功耗限制仍是2.5W,对于更高功率的设备,如打印机或显示,标准的USB功率极限通常不够,要求这些设备使用外部供电来满足其功率需求。

从系统观点看,当设备采用USB供电时,如果有一段时间没有使用该设备,则该设备必须进入“挂起”状态,此时最大吸收电流是500uA。

可以采用各种各样的设计方法设计系统来处理挂起模式,一种方法就是充分利用处理上的待机模式。当处理器进入待机模式时,可设置USB外设保持D+和D-引脚的状态,从该时刻开始,处理器都处于低功耗模式,直到USB引脚中的一个发生状态改变。这种状态的改变可触发外部调节器供电,然后处理器就可以上电,恢复状态,并从其停止的地方重新开始执行。

显然,有很多因素影响嵌入式应用的设备级和系统级功耗属性,通过对影响功率的关键因素的理解,对任何特定的应用,在减小功耗方面就能取得重大进展。

参考文献:

[1] David Katz and Rick Gentile. Embedded Media Processing, Newnes: Boston, 2006

[2] Seliverstov T. EE-339: Using External Switching Regulators with Blackfin(r) Processors, Analog Devices, Inc. Revision 1.0. 【R/OL】. [2008-5-14]. http://www.analog.com/static/imported-files/application_notes/EE-339.pdf

[3] Katz D, Gentile R, Tarkoff J. EPC-33: Understanding all of your options in Low-Power Embedded Processing Designs, Embedded Power Conference Proceedings, September 2008 [C], San Jose

[4] Sondermeyer J, Beauchemin J, Desai H. EE-334: Using Blackfin(r) Processor Hibernate State for Low Standby Power. Analog Devices, Inc. Revision 1.0. [R/OL]. [2008-5-5]. http://www.analog.com/static/imported-files/application_notes/EE-334_Rev1.pdf

[5] Analog Devices, Inc, ADSP-BF52x Blackfin(r) Processor Hardware Reference, Volume 1, Chapter 16, Revision 0.31[R]. May 2008

[v1]技术翻译错误

存储器相关文章:存储器原理

评论