基于Avalon总线TLC5628自定义IP核的开发

1 SoPC与IP核

本文引用地址:https://www.eepw.com.cn/article/90192.htm可编程片上系统(System on Programmable Chip,SoPC),是Altera公司提出的一种灵活、高效的SOC解决方案。他将处理器、存储器、I/O口、LVDS、CDR等系统设计需要的功能模块集成到一个可编程器件上,构成一个可编程的片上系统。他的实质是SoC(System on Chip)技术,与其他SOC技术相比,他的特点在于可编程性。

SoPC设计的关键技术之一是IP核(Intellectual Property Core),即知识产权核。IP核是指将一些在数字电路中常用但比较复杂的功能块,如SDRAM控制器、PCI接口都设计成参数可修改的模块,供用户直接调用。IP核有3个来源:EDA厂商提供、第三方提供、用户自定义。一般,EDA厂商及第三方提供的IP核都是功能上比较通用,但在实际SoPC设计过程中,用户常有特殊需求,这就要求用户用自定义逻辑实现所需的功能,因此在SoPC设计中,如何灵活地加入用户自定义逻辑就显得尤为重要。

2 Avalon总线

Avalon交换式总线是由Altera开发的一种专用的内部连线技术。Avalon交换式总线由SoPC Builder自动生成,是一种理想的用于系统处理器和外设之间的内联总线,其定义的内联线策略使得任何一个Avalon总线上的主外设都可以与任何一个从外设沟通。

Avalon接口定义Avalon外设与Avalon交换结构之间的连接。Avalon接口是一个灵活的接口,工程师可以只使用系统所需的几个信号进行数据传输。Avalon接口的一些显著特性如下:

(1)使用独立的地址、数据、控制线,提供与片上逻辑简单的接口;

(2)支持最高达128位的数据宽度,支持不是2的偶数幂的数据宽度;

(3)支持同步操作,所有Avalon外设的接口与Avalon交换结构的时钟同步,不需要复杂的握手/应答机制;

(4)支持动态地址对齐,可处理具有不同数据宽度的外设之间的数据传输;

(5)接口协议简单;资源占用少;

(6)Avalon接口性能很高,可达到每个时钟传输1次。

Avalon总线为用户提供了非常友好的接口,使系统搭建过程中的一些细节问题得到屏蔽,大大减轻系统搭建的工作量。此外,Avalon总线的“从外设仲裁”机制,消除了带宽瓶颈,实现了无与伦比的系统吞吐量。

3 用户自定义IP核的开发流程

用户自定义IP核按照对Avalon总线操作的不同可分为Avalon Master外设、Avalon Slaver外设及AvalonStreaming外设。用户开发的外设大多为Avalon Slaver外设,Avalon Master和Avalon Streaming外设的开发比Avalon Slaver外设要复杂,但开发流程相同。一个典型的Avalon外设的开发步骤如下:

(1)规划元件的硬件功能。如果采用微控制器来控制该元件,则规划访问该硬件的应用程序接口(API);

(2)在硬件和软件要求的基础上,定义一个恰当的Avalon接口(一般为Avalon从端口);

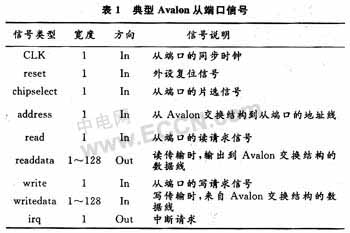

(3)使用硬件描述语言描述硬件逻辑。一个典型元件的硬件架构一般3部分组成:接口模块(avalon interface)作为顶层模块,定义总线接口信号;寄存器文件模块(register file)完成该元件与外部信号进行通信,提供访问与控制元件的逻辑界面;行为模块(task logic)实现元件的硬件功能。片上总线AvaIon从端口的信号都不是必须的,一个典型的Avalon从端口所包含的信号如表1所示。

(4)单独验证元件的硬件功能;

(5)写用于描述寄存器的C头文件来为软件定义硬件寄存器映像;

(6)写元件的驱动软件;

(7)把通过测试的源代码使用元件编辑器封装硬件HDL和软件文件,完成元件定制。

4 TLC5628自定义IP核的开发

4.1 TLC5628 D/A转换器

TLC5628是TI公司生产的8位8通道串行D/A转换器,采用5 V单电源供电,输出电压范围可编程。输出电压编程范围由RNG位控制,当RNG位为1时,输出电压范围为0~2×Vref;当RNG位为0时,输出电压范围为0~Uref。A2A1A0位表示D/A输出通道选择,000~111分别对应第1~8通道,D7~D0是输出数据位。TLC5628D/A转换器时序图见图1。

4.2 硬件部分构建

4.2.1 接口模块的设计

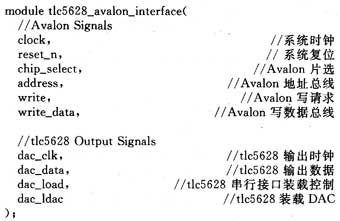

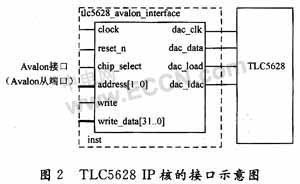

根据TLC5628 D/A的功能描述,该模块所需的Avalon总线输入信号为chipselect,CLK,address,write,write-data及reset信号,是一个典型的只向Avalon总线写数据的模块。而模块输出则为dac_clk,dac_data,dac_load及dac_ldac信号,分别对应TLC5628 D/A的串行输入时钟,串行输入数据,串行载入及更新输出控制,其对应框图(也即TLC5628 D/A与Avalon总线的接口图)如图2所示,该接口模块定义了总线接口信号,作为顶层模块。

Avalon总线接口设计文件的端口说明部分如下:

4.2.2 寄存器文件模块

寄存器文件模块实现该元件与外部信号进行通信,提供了访问与控制元件的逻辑界面。

在寄存器文件中,Avalon总线的地址信号(address)为2位,address为00表示分频寄存器,用以产生串行D/A的输入时钟,32位分频寄存器数据位只写;address为01表示数据寄存器,32位数据寄存器数据位只可写,address为10和11位保留。

Avalon总线数据信号在chipselect和write信号的控制下,向寄存器写入分频数和数据位。当向分频寄存器写入数据时,32位数据表示分频数;当向数据寄存器写入32位数据时,保留后12位数据(8位数据位+RNG位+3位通道选择位)。该控制过程由同步有限状态机实现。

4.2.3 行为模块的实现

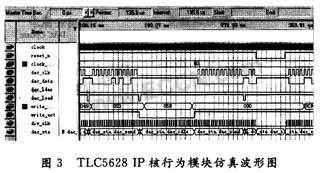

行为模块实现元件的硬件功能,接收来自Avalon总线的数据,在写使能信号的控制下,向TLC5628 D/A输入寄存器写入通道选择及数据位。数据的发送及存储由同步有限状态机实现。在写数据信号使能时,输入数据在串行时钟的控制下依次写入数据寄存器,当12位数据全部写入后,内部标志位dac_dat_send_finish置位,数据发送完成,进入数据锁存状态,此时置位Load信号(LDAC信号一直为低),DAC更新输出数据。在QuartusⅡ6.0环境下,基于EPlC6Q240C8器件的仿真波形如图3所示。

4.3 软件设计

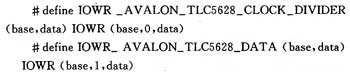

软件设计包括寄存器头文件的设计、驱动软件及测试程序的设计。寄存器头文件avalon_tlc5628_regs.h定义了对TLC5628的寄存器进行写操作的宏。IORD和IOWR是硬件抽象层(HAL)提供的2个访问寄存器的C语言宏。下面2行代码分别是对分频寄存器和数据寄存器的写操作宏。

驱动软件包括avalon_tlc5628.h和avaIon_tIc5628.c文件。avalon_tlc5628.h定义了驱动函数的原型及常量,avalon_tlc5628.c则实现驱动函数的功能。avalon_tlc5628.c中定义了2个函数,一个是TLC5628初始化函数avalon_tlc5628_init(),完成TLC5628初始化,设置串行时钟、通道选择、电压输出范围编程及数据初始化;另一个是TLC5628输出数据更新函数avalon_tlc5628_update_data(),用以改变输出的通道数和电压值。

测试程序调用驱动函数对硬件设计和软件设计进行测试。如:avalon_tic5628_init(TLC5628_BASE,250,0x0),设置TLC5628的串行输入时钟为100 kHz;avalon_tlc5628_update_data(TLC5628_BASE,0x340),设置TLC5628的第二输出通道DACB输出的电压为2×VREF/4。

4.4 封装和发布

在软件和硬件设计完成后,通过SoPC Builder提供的“元件编辑器”进行封装。当HDL文件加入后,指定接口模块为顶层模块,同时指定端口说明中的信号类型。如CLK被指定为“clk”类型,address被指定为“address”类型,dac_lclk,dac_load,dac_data及dac_ldac被指定为“export”类型。之后,SoPC Builder会在当前目录下生成tlc5628_avalon_interface子目录。子目录中包含class.ptf文件、脚本文件及源代码文件。这样,TLC5628 IP核的封装和发布就完成,其他用户也就可以共享TLC5628 IP核。

5 结语

在SoPC设计中,设计人员可以灵活方便地加入IP核,减轻工程师开发负担,避免重复劳动。本文通过介绍基于Avalon总线TLC5628自定义IP核的开发详细阐述SoPC设计环境下用户自定义IP核的开发流程,对于开发较复杂IP核有一定的借鉴作用。

c语言相关文章:c语言教程

评论