集成压控振荡器的可靠性设计与分析

0 引言

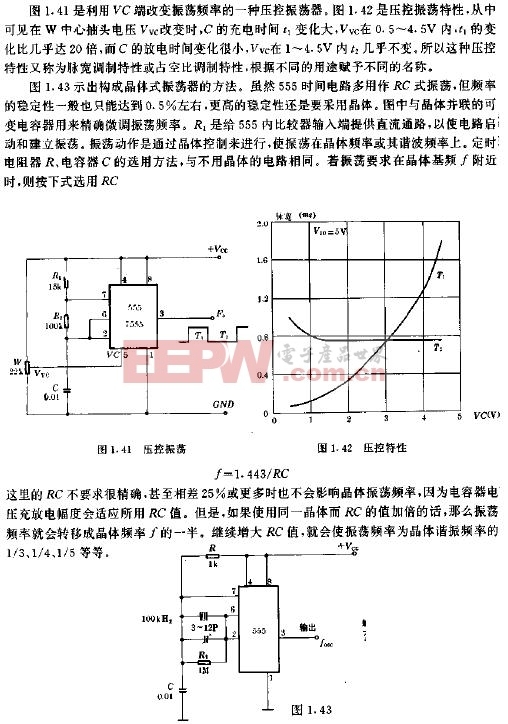

本文引用地址:https://www.eepw.com.cn/article/89220.htm宽带微波扫频源和微波频率合成器是微波设备的核心部件,宽带、高性能、小型化、高可靠是现代装备系统的必然要求。集成压控振荡器(VCO)作为关键器件,其性能直接影响整机性能的优劣,宽带VCO的可靠性和稳定性在很大程度上制约着电子装备和系统的可靠性和有效性。因此,设计稳定可靠的宽带VCO成为当前微波领域的重要课题之一。可靠性设计已成为混合集成电路研制过程中的一个非常重要的环节,而产品的可靠性源自于可靠的设计和严格的工艺在线质量控制。

1 集成VCO的可靠性分析

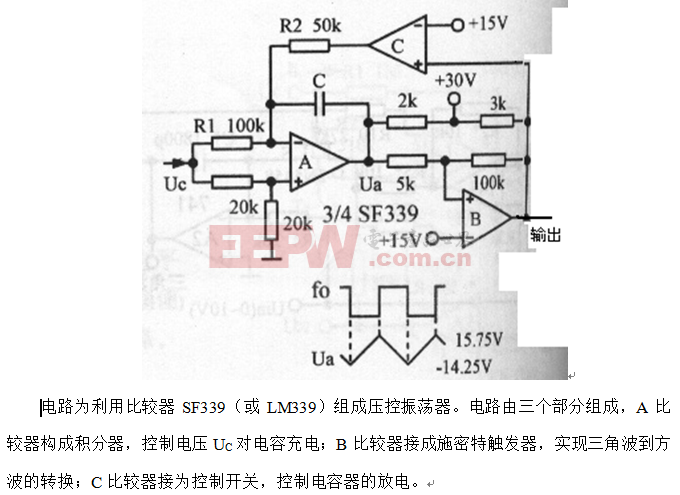

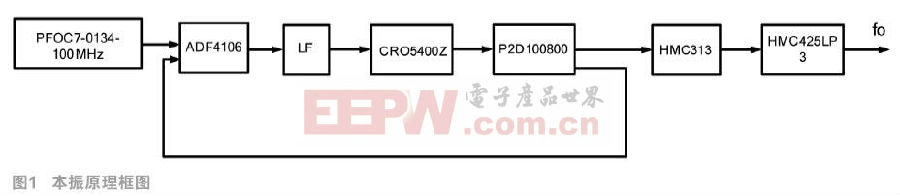

微波混合集成VCO采用薄膜混合集成电路工艺,通过多芯片组装技术将有源器件和无源元件等组装于微波管壳之中。混合集成技术可调整电路的参数,实现不同的电路功能,在电路实现上具有较强的灵活性。其绝缘基片一般采用低损耗陶瓷材料,有源器件采用半导体芯片,在实现电路小型化的同时,电性能指标一般比单片电路有明显的优势,其外形封装及内部结构如图1所示。

VCO电路是运用负阻振荡原理、变容二极管调谐的LC振荡器。电路调试完成后密封封装,按照混合集成电路通用规范GJB 2438A-2002及企军标规定的内容进行筛选和鉴定检验,其主要试验有温度循环(-65~+150℃,100次)、机械冲击、恒定加速度、随机振动、热冲击、稳定性烘烤、耐湿、盐雾、ESD、水汽含量、DPA、PIND等。一些航天设备还要进行核辐照试验、扫描电镜检查等。要提高VCO产品的可靠性,首先要从可靠性设计着手。设计人员应该掌握VCO在各种条件下的失效模式及相应的失效机理,在进行电路设计、热学设计的同时应考虑到各种环境条件的影响。基于集成宽带VCO的工作原理、工艺结构和使用环境要求,本文从元器件及材料的选择、电路设计、工艺设计及关键工艺控制等几个方面进行了可靠性设计研究。通过电路及工艺优化设计、失效分析,解决宽温工作、抗ESD设计、内部水汽含量控制、键合引线和芯片剪切强度等问题,对于提高压控振荡器产品的可靠性具有重要意义。

2集成宽带VCO的可靠性设计

2.1 元器件和材料的选择与质量控制

(1)为确保VCO电路模块的可靠性,对所用元器件分别从电性能、热性能、可焊性和可靠性各方面综合考虑。对重要的元器件要有工艺验证数据、试验考核数据等,作为设计和选用的依据。

(2)在微波薄膜基片材料中,最为常用的是Al2O3含量为99.6%、表面光洁度为1~6μinCLA的陶瓷基片,其介电常数εr在9.9左右,微波损耗低。10 GHz时损耗角tgδ<5×10-4,适用于微细加工的薄膜工艺。

(3)严格控制MOS电容制作工艺。MOS电容采用SiO2及Si3N4双层介质,具有零温漂,同时减薄衬底、加厚电极金层、减小串联电阻、降低损耗。MOS电容装配前经过100 V耐压测试,操作过程中注意防静电。

2.2优化电路设计

优化设计可以提高产品的固有可靠性,在满足VCO产品性能要求的前提下,尽量减少电路的单元数。将振荡电路设计在最稳定的工作状态,以保证电路在所需的频率范围内能保持足够大的负阻以稳定振荡。借助CAD优化设计输入电路、反馈电路及输出匹配网络参数,获得带内最大负阻特性。另外还要考虑集成宽带压控振荡器在环境温度-55-125℃能正常工作,如果VCO设计或调试状态临界,则会造成高低温工作时出现停振、杂波、分频等现象,这种失效模式比较常见。

2.3电路降额设计

根据不同工程的降额等级要求,对宽带VCO进行降额设计。电路基片要保证薄膜功率密度(W/cm2)满足降额要求,设计适当的NiCr薄膜面积及其电阻值,以保证其有足够的功率容量。有源器件的功耗应有降额设计,比如在4~8 GHz VCO中,振荡管的最大直流功耗为500 mW,而实际使用中仅为200 mW左右;缓放电路使用的FET最大功耗为430 mW,其在4 V/70 mA的偏置下输出为21 dBm,实际电路要求的功率为10 dBm,因此其工作偏置点远小于21 dBm下的工作点,仅为3 V/30 mA左右,源漏电压及漏电流都有较大的裕量,约为额定值的一半。

2.4电路热设计及低功耗设计

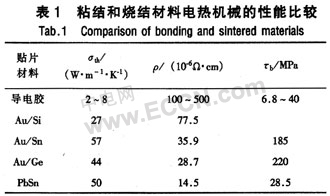

在版图的热设计上,应将发热较多的的元件如电阻和有源器件在基片上分散分布,以利于散热,降低结温。在保证VCO能正常工作状态下,尽量降低有源器件功耗,并研究管壳热设计和热分布分析等技术,减小芯片到管壳间的热阻。 为了降低热阻,基片与有源器件都采用烧结工艺。半导体芯片及元件组装到基片、管壳载体上,实现的方法主要有导电胶(epoxy)粘接和共晶(eutectic)烧结两种。导电胶粘接的方法具有工艺简单、效率高、成本低、可修复、低温粘接、对管芯背面金属化无特殊要求等优点,但在微波频率高端或微波大功率时,由于导电胶粘接的电阻率ρ大(100~500 μΩ·cm),热导率σth低(2~8 W/m·K),造成微波损耗大、热阻大,其功率性能及可靠性等方面将受到影响。而共晶烧结方法则具有电阻小、热阻小、剪切强度τb大和可靠性高等优点,因而在高可靠模块中被广泛应用。两种方法性能对比是表1。

由表1可以看出,共晶烧结的热性能、电性能及机械性能大大优于导电胶粘接。目前共晶烧结技术比较成熟,选择合适的烧结方法,对共晶烧结技术采取一些检测手段,如红外热像分析仪和X射线透视仪,有助于电路的可靠性分析。通过用红外热像分析仪测得的振荡管在壳温为70℃时的最高结温为110℃,薄膜电阻的最高温度为115℃,从而保证了其长期可靠工作。

2.5集成VCO的抗ESD设计

集成宽带VCO内部集成的MOS电容、有源半导体芯片为静电敏感器件,其ESDS等级为I级。通过改进电路设计,优选元器件和工艺过程防静电控制措施,提高VCO的抗静电击穿能力,是提高VCO可靠性的重要环节。

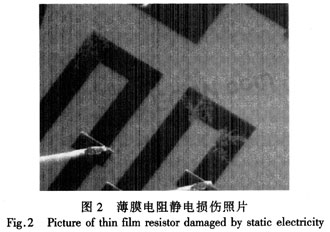

通过对VCO做静电摸底试验与开帽分析,ESD敏感部位定位在MOS芯片电容、薄膜电阻和硅微波双极晶体管上,这是影响电路抗静电能力的主要因素。VCO电调端和输出端均有MOS芯片电容,MOS电容的静电损伤是其薄弱点。在实际应用中,电调端电容与输出端电容是最容易被静电损伤的元件,从而造成电调端与输出端电容漏电。此外,电调端细条NiCr薄膜电阻直角拐点处也是静电损伤的薄弱区,如图2所示。

2.5.1 ESD损伤机理

对于半导体器件来说,主要有两种不同类型的损伤:过电流损伤和过电压损伤。

2.5.2 ESD失效模式

ESD失效模式有两类:致命失效和参数退化失效。致命失效即pn结局部反向击穿,形成熔点。参数退化失效是指静电能量不足以使pn结反向击穿,只造成局部损伤,如pn结的再扩散、氧化层损伤等,但如果经过多次静电损伤,将导致器件性能恶化,大大降低寿命。

2.5.3提高电路抗静电击穿能力的技术措施

(a)根据过电压失效模式及硅双极晶体管的特点,在振荡电路中采取吸收网络,为过电压提供泄放通道;同时考虑过电流,在输入端和发射极串接小电阻起限流作用。 (b)电路内部采用的MOS芯片电容的优点是体积小、温度稳定性能好、Q值高,但抗静电击穿能力较差。根据实际试验数据统计,对于一般的MOS电容(介质厚度SiO2150 nm、Si3N4120 nm,芯片面积0.8 mm2)抗ESD能力为500~1 000 V。因此,根据试验结果和分析情况,对内部MOS电容进行了改进,在体积允许的范围内,增大电容面积,同时增加SiO2和Si3N4介质层厚度,保持电容值基本不变,以提高MOS电容的静电击穿电压。

(c)装架前芯片严格镜检。对平面螺旋电感等间隔较近的光刻金属条的边缘严格控制,剔除有尖峰状毛刺的图形基片,避免由此造成静电薄弱区。

此外,电路设计上还应避免薄膜电阻条的直角拐点产生,混合电路膜电阻设计原则如下

R=ρd/s

式中:R是膜电阻;d是长度;s是横截面积;ρ电阻率。

等比增加d和s,R不变,但在静电放电时单位体积内耗散功率减少,提高抗静电能力。

d)产品的生产过程中完善防静电措施,硬件条件符合防静电工作区的要求,工作台面电阻、接地线对地电阻等周期性检测,防静电腕带并定期测试,配备人体静电测试仪和台面静电测试仪等必要的检测装置,产品的周转、存放、包装均采用防静电存储盒、架等。

2.6宽带VCO的耐环境设计

集成宽带VCO环境适应性试验有温度循环(-65~+150℃,100次)、机械冲击、恒定加速度、热冲击、稳定性烘烤、耐湿、盐雾、水汽等,因此在元器件与材料选择、内部工艺设计及控制等方面进行细致设计、严格把关。

在研制和摸底试验中出现过PIND失效、离心时元件脱落甚至基片脱落、离心后基片产生裂纹、水汽含量超标、剪切力达不到要求等失效现象,其主要原因有以下几个方面:

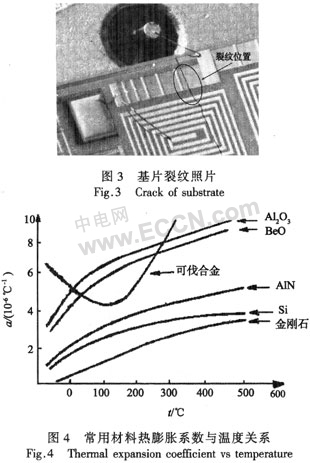

(1)基片表面清洗不干净导致金属颗粒附着在基片上,调试时键合丝有残留,内部材料经过温循环、离心后产生金属颗粒,储能焊封帽时的金属飞溅物都可能导致PIND不合格,内部存在金属颗粒,在一定情况下引起电路失效。(2)芯片剪切强度小,说明粘接强度低。器件的耐机械冲击、耐振动、耐离心加速度的能力就低,严重时会使芯片脱落。基片表面存在沾污、元器件电极有沾污、芯片背面有残留胶膜等,造成与粘接剂浸润性变差也可能造成芯片脱落。(3)混合电路的工艺特点是采用多种材料,涉及到粘接和烧结材料、元器件、基片及金属膜、管壳等,这些材料的热膨胀系数往往存在差异,在电路生产和环境试验过程中应力积累,导致基片出现裂纹,如图3所示。图4是常用材料热膨胀系数α与温度t的关系,从中可以看出可伐材料热膨胀系数随温度变化最大,因此它与其他材料的合金贴装,容易产生裂纹。 (4)产品所用的贴片胶、内部器件本身的水汽含量、内部器件及基片表面的水汽吸附都会影响器件封装内部的水汽含量。水汽含量高可能会导致以下三种失效模式:金属位移、腐蚀和器件性能不稳定。

针对以上的问题和失效模式,本文主要采取了以下解决措施:

(1)加强电路基片的表面处理,改善基片与粘接剂的附着力。组装前100%的基片进行有机溶剂和水的超声清洗,干燥后存储于氮气柜中,保证基片清洁无沾污。封帽前严格镜检并清除多余物,设置最佳的封帽工艺参数,避免局部打火形成的金属飞溅物。

(2)选用性能优良的导电胶,考虑高低温的稳定性问题以及抗热疲劳能力,粘接材料的固化温度和封帽前烘温度高于成品电路温度循环和温度冲击的最高温度。

(3)进行了不同材料的热膨胀系数的研究,选择较为匹配的材料和工艺,设计柔性缓冲层,如软焊料的选用、限制基片尺寸等。 (4)优化封帽工艺环境和条件,试验不同的前烘时间和温度对水汽含量的影响,从而确定最佳的封帽前预烘条件。在电路中不采用易产生降解水或有机气体的粘接剂,控制电路内部水汽含量小于5.0×10-3。

2.7严格的工艺在线监控

确定严格的工艺规范和工艺在线监控和检测手段。集成VCO制作工序复杂、工艺线长,影响因素较多,每一道工艺必须保持状态稳定,规范工艺操作程序,实施工艺在线监控,完善产品的检测手段,才能保证最终产品的成品率和可靠性。

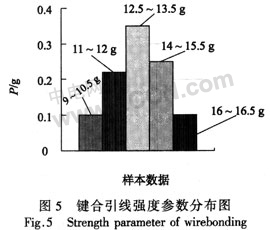

对关键工序键合工艺进行工序能力指数分析和控制,采用"试装"的方法,先进行小批量的试键合,获得一定量的数据,计算CPL≥1.33后再进行正式生产,保证正式产品的内引线键合强度的一致性。本文引线键合强度分布是图5,12.5~13.5 g出现的概率(P)最大。

4 结语

通过对集成宽带VCO的可靠性设计、可靠性增长试验及研究,使VCO的可靠性有了很大的提高。目前国内的混合电路可靠性水平与国外还有一定的差距,还需要在可靠性理论研究、电路设计、工艺水平等方面继续开展深入细致的工作。

晶体管相关文章:晶体管工作原理

lc振荡电路相关文章:lc振荡电路原理 晶体管相关文章:晶体管原理 漏电开关相关文章:漏电开关原理 网线测试仪相关文章:网线测试仪原理

评论