基于SOC应用的运算放大器IP核设计

摘要:基于SOC应用,采用TSMC 0.18μm CMOS工艺,设计实现了一个低电压、高增益的恒跨导轨到轨运算放大器IP核。该运放采用了一倍电流镜跨导恒定方式和新型的共栅频率补偿技术,比传统结构更加简单高效。用Hspice对整个电路进行仿真,在1.8V电源电压、10pF负载电容条件下,其直流开环增益达到103.5dB,相位裕度为60.5度,输入级跨导最大偏差低于3%。

关键词:运算放大器;轨到轨;共栅频率补偿;IP核

1引言

在SOC的模拟集成电路设计中,使用简单的电路结构来实现高性能成为趋势,SOC的设计核心是IP核设计。运算放大器是模拟电路中最重要的电路单元之一,广泛应用于如数/模、模/数转换器和开关电容电路中[1-2]。随着电源电压的不断降低,为了提高动态范围,轨到轨(Rail to Rail)设计变得十分重要。

通常采用互补差分对实现输入级共模电压的Rail to Rail, 但其跨导在整个输入范围内变化接近一倍[3],这使得频率补偿变得很困难,运放稳定性变差。Rail to Rail运放通常需要两个电容作为Miller补偿以提供足够的相位裕度[4],这不仅会占用大量的面积,也限制了单位增益带宽。

从IP核的设计角度出发,本文所设计的运放采用一倍电流镜跨导控制电路恒定输入级跨导,这种方式结构简单,电路芯片面积小,同时也不会增加输入级的噪声。输出级采用AB类推挽结构,它能够在低压下实现全摆幅的输出,并且可以在保证低失真的情况下,得到较高的电源效率。针对AB类输出级的特殊结构,采用了一种新型的共栅频率补偿技术[5],可以消除右半平面低频零点,而且只需要一个补偿电容,不仅提高了单位增益带宽,也节省了芯片面积。仿真结果表明,该运放能够在1.8V的低电源电压下稳定工作,非常适合于低电压SOC应用。

2电路结构和原理

2.1 Rail to Rail输入级及跨导控制

为了使运放的共模输入在整个电源范围内变化时电路都能正常工作,采用NMOS 管和PMOS管并联的互补差分输入对结构来实现输入级的Rail to Rail。根据输入共模电压的不同,输入级可分为三个工作区域[6]:当共模输入电压接近VSS时,仅PMOS输入对导通,输入级跨导为 ;当共模输入电压接近VDD时,仅NMOS输入对导通,跨导为 ;当共模输入电压处于中间值时,p 沟和n 沟输入对均导通,跨导为:

![]()

由上式可知,Rail-to-Rail 结构的输入级跨导会在整个共模输入范围内变化将近一倍。若将其运用于带有反馈回路的运放中,其环路增益也变化近一倍,必将引起失真的增大。当输入级跨导增大一倍,则单位增益频率增大一倍,从而导致相位裕度减小,运放稳定性变差,这也造成了频率补偿很难实现。所以必须将其改进以恒定跨导。

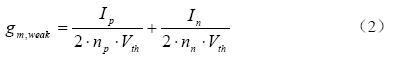

本文设计的Rail-to-Rail 输入级工作在弱反型区,MOS管总输入跨导可由下式给出:

其中, 是PMOS输入对的尾电流, 是NMOS输入对的尾电流, 分别是PMOS和NMOS输入对的弱反型斜率因子。

由(2)式可知,工作在弱反型区的MOS管跨导与漏电流成正比。所以可通过保持互补输入对总的尾电流恒定来稳定 。假设两类晶体管的弱反型斜率因子相同,要得到恒定的 ,其总的尾电流应满足:

![]()

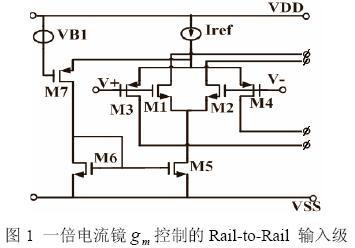

满足上述要求的Rail-to-Rail 输入级结构如图1所示,由通过电流开关M7和一倍电流镜M5-M6来实现输入级的gm 控制。若共模输入电压较低,电流源 偏置于PMOS输入对M3-M4,仅有PMOS输入管对输入信号有放大作用。当共模输入电压升高到(VDD-VB1)时,电流开关M7 就会分走 的部分电流,并通过电流镜M5-M6 将其注入到NMOS输入对中。因此,输入对总的尾电流恒为 。若共模输入电压进一步增大,PMOS输入对截止,电流开关使得 通过电流镜全部注入到NMOS输入对。从而使 在整个共模输入范围内保持恒定。但由式(2)可知, 还与弱反型倾斜因子n有关。若NMOS与PMOS输入对的弱反型斜率因子不等,仍会引起 的变化,可通过改变电流镜的增益系数来得到补偿。

由于电流开关和电流镜所占面积相对较小,该 控制电路几乎不会增加输入管的尺寸大小,因此电路芯片面积小、功耗低,非常满足IP核设计的要求。还有另一个优点是不会增加输入级的噪声,因为在gm控制电路中生成的噪声夹杂在互补输入对的尾电流中,可认为是共模信号。对Rail-to-Rail输入级来说,若输入管匹配,gm控制电路所产生的噪声就可以忽略掉。

2.2 Rail-to-Rail输出级及共栅补偿技术

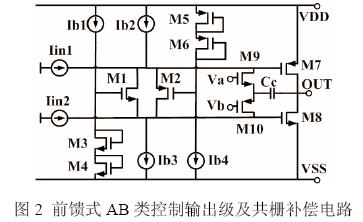

在Rail-to-Rail输出级中,AB 类传输函数可通过保持输出管栅极间电压恒定来实现。采用带有前馈AB类控制的推挽输出结构,它能够在低压下实现全摆幅的输出,并且可以在保证低失真的情况下,得到较高的电源效率。

用晶体管耦合直接前馈通路实现的AB 类前馈式输出级如图2 所示。M7、M8为Rail-to-Rail 输出管,M1、M2 组成晶体管耦合的AB 类控制电路。Iin1和Iin2为同相位的小信号电流源。电路中的两个回路M2-M7 和M1-M8控制输出管的静态电流。当一个输出管电流非常大时,另一个输出管能够保持一个最小值,而不是截止为零,避免了从截止到导通所需要的时间延迟,也减少了交越失真。

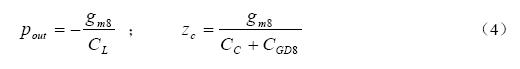

通常Rail-to-Rail运放是多级放大器,需要两个(或两个以上) 电容作为Miller 补偿以提供足够的相位裕度,这不仅会占用大量的面积,也限制了单位增益带宽;而且多级放大器作为输出缓冲器时,电路的稳定性还容易随负载电容大小的变化而改变,产生震荡。Miller补偿要求在M23 和M24 栅漏两端分别接入两个补偿电容,其输出极点可简单的表示为(假设gm7等于gm8, CL 是负载电容) :

由于电容的前馈通路,Miller 补偿引入了一个右半平面零点zc,该零点减小了相位裕度,同时也限制了单位增益带宽。

由于电容的前馈通路,Miller 补偿引入了一个右半平面零点zc,该零点减小了相位裕度,同时也限制了单位增益带宽。

如图2所示,针对特殊的AB类输出级,采用M9,M10和电容CC组成的共栅频率补偿结构,可以阻止通过电容的前馈电流,并将右半平面零点移至高频,同时也减少了一个补偿电容,节省了芯片面积。假设只考虑晶体管M8 所构成的NMOS 共源输出级,通过小信号分析可以得到,该电路引入了一个位于左半平面的零点:

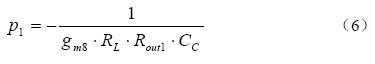

整个放大器主极点可以近似等于:

其中Rout1为第一级放大电路的输出电阻,RL为负载电阻,对于较大的RL ,输出极点可以近似为:

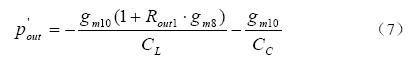

从式中看出,输出极点增大了约gm10Rout1倍,增加M10 (和M9) 的跨导还可将此极点移至高频,因此采用较小CC就能实现频率补偿,获得较高的单位增益带宽。但是,增加gm9, gm10将会导致M9 和M10 的漏电流增加,从而减少流经M1 和M2 的电流,进一步减小M1和M2的源漏端的饱和压降Vdsat,而流经M7和M8的电流将增加,输出阻抗减小,最终导致放大器开环增益的降低。此外,增大gm9 , gm10还会增加等效的输入噪声和放大器的功耗。因此M9、M10的设计只需使得两个极点分离足以满足稳定性所需的相位裕度即可。流经M9 和M10 的漏电流总是相等,M9和M10的引入并不会影响放大器总体的失配;同时(7)式也说明采用较小的补偿电容CC 还可以减少负载电容CL 的增加对电路频率特性的影响。

3整体电路实现与仿真

综上所述,电路的整体实现结构如图3所示,由晶体管M18-M22构成的电流镜和由M28-M31构成的电流镜为整个电路提供偏置电流。为了减小输入失调,尽量增大输入晶体管面积,减小其有效栅源电压,同时尽可能减小电流镜和电流源的宽长比。通过减小电流开关M15的宽长比将失调变化扩展到整个共模输入范围,可以增加共模抑制比。

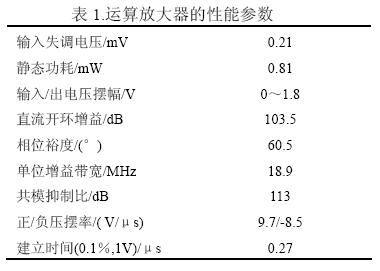

电路采用TSMC 0.18μm 1P6M CMOS数模混合工艺,基于BSIM3V3 Spice模型,10pF电容负载的条件下,用Hspice对整个电路进行仿真,电源电压为1.8V,偏置电压为0.8V。

输入级跨导随输入共模电压变化的结果如图4所示,可以看出,输入级跨导大约为290μS,在整个输入共模电压范围内只变化3%,基本保持恒定。在0~0.4V,PMOS差分输入对导通,NMOS差分输入对截止,输入级跨导为PMOS输入对的跨导;在0.9~1.8V,输入级跨导为NMOS输入对的跨导;在0.4~0.9V,PMOS和NMOS差分输入对同时导通,电流开关抽取电流会引起跨导变化,主要是由NMOS和PMOS差分输入对的宽长比以及弱反型斜率因子的不同引起的。

该运放的频率特性如图5所示,整个电路的直流开环增益为103.5dB,相位裕度为60.5度,单位增益带宽为18.9MHz。相比之下,采用传统miller补偿其带宽只有9.5MHz。

该运放的频率特性如图5所示,整个电路的直流开环增益为103.5dB,相位裕度为60.5度,单位增益带宽为18.9MHz。相比之下,采用传统miller补偿其带宽只有9.5MHz。

整个放大器的设计结果如下表所示,运算放大器的整体性能较好,并且能够在1.8V低电压下工作,功耗低,芯片面积也大大节省。

4结束语

随着电源电压的降低以及芯片集成度的增加, 以IP核形式的Rail to Rail运算放大器设计较有优势,它可以节省成本和缩短系统设计周期。本文基于0.18μm CMOS工艺设计了一个恒跨导Rail to Rail运算放大器,整个电路结构简单紧凑,功耗低,非常适合做成SOC的IP核。

本文作者创新点:

(1) 从IP核的角度进行运算放大器的设计,使其更具有应用价值。

(2) 采用一倍电流镜方式进行跨导控制,和新型的共栅频率补偿技术,使整个电路结构简单紧凑,适合与其它电路模块集成应用于SOC。

参考文献:

[1] Trung K N, Sang G L. Low-voltage, low-power CMOS operation transconductance amplifier with Rail-to-Rail differential input range [J]. IEEE ISCAS. 2006; 10:1639-1642

[2] 候卫卫,冯全源.一种高性能单位增益放大器[J].微计算机信息,2007;2-2:291-293

[3] Juan. M. Carrillo, Francisco J, Duque-carrillo, et al. Constant-gm constant-slew-rate high-bandwidth low-voltage Rail-to-Rail CMOS input stage for VLSI cell libraries [J]. IEEE International Symposium on Circuits and Systems, 2003; 38(1): 165-168

[4] Loikkanen M, Kostamovaara J. Low voltage CMOS power amplifier with rail-to-rail input and output [J]. Analog Integral Circuits Process, 2006, 46(2) :183

[5] 王为之,靳东明. 一种采用共栅频率补偿的轨到轨输入/输出放大器[J]. 半导体学报,2006;27(11):2026-2028

[6] 杨银堂,李晓娟,朱樟明等. 低压低功耗运算放大器结构设计技术[J]. 电路与系统学报,2005;10(4):95-101

注:本课题受国家自然科学基金和部委预研基金项目支持,其经济效益分别为27万和15万元,目前处于研究过程中。

作者简介:唐重林(1984-),男(汉族),江西安远人,硕士研究生,主要从事模拟集成电路设计方向研究;柴常春(1960-),男(汉族),教授,博士生导师,主要从事新型半导体器件与材料,集成电路设计方向研究。

评论