廉价可编程逻辑辅助设计工具魅力犹存

——

廉价可编程逻辑辅助设计工具魅力犹存

由于经济压力,人们对使用 100 美元以下的低价位的设计工具的兴趣越来越高;而另一方面,也是由于经济原因市场上能满足这种低价位的设计工具越来越少。好在经过仔细的搜寻,人们还是可以找到一些物美价廉的工具的。

在《EDN China》杂志上讨论对PLD和 FPGA 免费或廉价开发支持的专题文章,最近的一篇发表在 1997 年 (参考文献 1)。在重温该文和随后在《技术前沿》栏目发表的上一篇关于该主题的文章时,我们发现上述两篇文章所提到的许多公司已不再从事或已大大地压缩了可编程逻辑业务活动 (参考文献 2)。硅片供应商 AMD公司和朗讯科技公司,以及后来的杰尔系统公司,都将其产品系列出售给Lattice 半导体公司;Anachip 公司收购了 ICT公司;摩托罗拉公司终止了 FPGA 开发活动;STMicroelectronics公司收购了Waferscale Integration公司;Xilinx 公司接管了飞利浦公司的产品系列。

在《EDN China》杂志上讨论对PLD和 FPGA 免费或廉价开发支持的专题文章,最近的一篇发表在 1997 年 (参考文献 1)。在重温该文和随后在《技术前沿》栏目发表的上一篇关于该主题的文章时,我们发现上述两篇文章所提到的许多公司已不再从事或已大大地压缩了可编程逻辑业务活动 (参考文献 2)。硅片供应商 AMD公司和朗讯科技公司,以及后来的杰尔系统公司,都将其产品系列出售给Lattice 半导体公司;Anachip 公司收购了 ICT公司;摩托罗拉公司终止了 FPGA 开发活动;STMicroelectronics公司收购了Waferscale Integration公司;Xilinx 公司接管了飞利浦公司的产品系列。

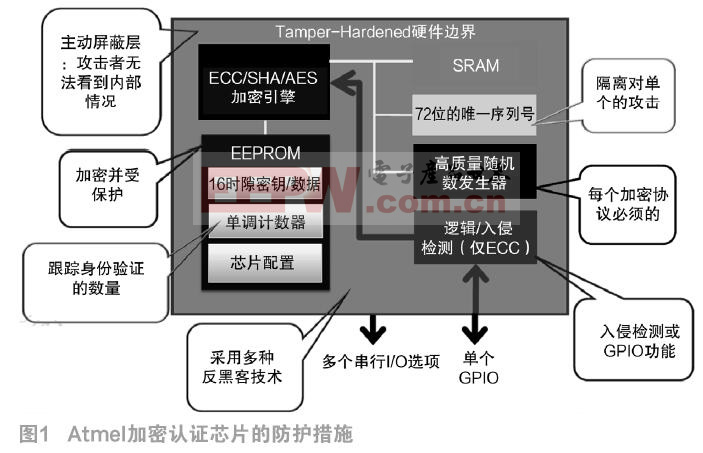

在作者准备本文时,Atmel 公司和 Cypress半导体公司都没有回答作者多次要求它们提供信息的请求,由此看来,两家公司的可编程逻辑产品系列难以为继的传闻也许是真的。由硅片业务转向软件的Xilinx 公司收购了 Data I/O 公司的 Synario 部。这一并购活动在某种程度上反映了在电子行业的任何日趋成熟的领域内发生的达尔文之"适者生存"趋势。电子行业中的高科技低迷状态,目前尚无好转的迹象,这就加快了并购的步伐。正是这种低迷状态不断地给业者施加愈来愈大的压力去压缩系统设计开发周期和材料成本,从而使得如今谈论 PC 软件免费或几近免费,比 1997 年更合时宜。(本文还把过去文章讨论的重点从软件拓宽到包括其它开发工具。)

然而,你的需求与其余的芯片供应商和软件供应商的需求是不一致的,因为这些供应商不愿意提供免费的或廉价的开发工具,当他们的投入回报还不清楚时尤其是如此。它们乐意提供限时或只有部分关键功能的产品版本给你试用,但是,要想进行有意义的开发工作,并将你的设计投产,你最终不得不打开你的钱包,支付几百乃至几千美元的费用。当然,这一规则的例外是有的,就像计算机用户厌烦不断向微软送钱而转向开放源代码操作系统和应用程序一样,开发工具的用户也许会加入开放源代码运动,以有助于其可编程逻辑开发工作。

软件援助

厂商提供的设计套件的入门级版本通常支持产品系列和器件中具有有限功能的一个子集。例如,Altera 公司的可免费下载的 Quartus II 网络版软件 2.2 版,它针对的是主流的 Max 3000 型和 Max 7000 型 CPLD 器件,以及 Acex、Cyclone 和 Flex 6000 型FPGA,只适用于一个或少数几个高端 FPGA 系列。它支持基于原理图和文本的设计输入、Verilog 和 VHDL 综合、功能模拟和定时分析、布局和布线、以及通过 ByteBlaster、ByteBlasterMV 和MasterBlaster 电缆进行的器件编程。

Altera 公司提供的另一套免费工具集是 Max+Plus II Baseline,它包括较老的 AHDL 设计语言和 Classic 产品系列。Altera 公司的设计软件起步者套件 CD-ROM 光盘含有 Quartus II 网络版和 Max+Plus II Baseline。如果签约订购Quartus II ,你就可以得到对 Altera 产品库中全部器件的支持,另外还有行为建模与测试台、LogicLock 基于组件递增设计、较快的拟合算法、Tcl 文稿编排程序以及 SignalProbe 递增式布线方面的支持。

与Altera 公司免费软件对等的Xilinx公司产品是 ISE WebPack 和 WebFitter,两者均采用该公司收购两家综合厂商 Minc 公司和 Synario 公司时获得的技术 (参考文献 3)。ISE WebPack 在概念上与 Quartus II 网络版相似,它支持 Xilinx 产品系列的一个子集,并且只能从 Xilinx 公司网站上获得技术支持服务。ISE WebPack 既不能与 Core Generator 和 FPGA Editor 这些工具发生交互作用,也不包含 ChipScope Pro 设计验证。与 Quartus II 网络版不同,ISE WebPack 不仅允许 Verilog 和 VHDL 设计输入,还允许 Abel 语言综合。

所有的 ISE 变异都可以与 Mentor Graphics 公司开发的免费 ModelSim Xilinx Edition 模拟程序选件接口,ISE WebPack 的其余免费附件有 HDL Bencher 自动测试台生成程序、StateCAD 自动状态机设计生成程序、ChipView 前后拟合图形实用程序 (用以分配和观察引脚和逻辑布局),以及 Xpower 图形功率分析工具。Xilinx 公司也可提供基于电子数据表和 Web 的功率分析工具 (参考文献 4)。ISE WebPack 只能在 Windows 操作系统下运行,而 WebFitter 的基于 Web 的接口还可以支持 Unix 和其它与浏览器兼容的操作系统。所有这些工具都只适用于 Xilinx 的 CPLD。该软件很容易访问报表、注释和元器件报价数据。WebFitter 还允许转换用其它工具和其它制造商的器件生成的设计。

如果 Altera 公司和 Xilinx 公司正在提供可免费下载的设计软件套件,那么可以肯定,第三家最大的可编程逻辑供应商 Lattice Semiconductor 公司也在这么做。ispLever 起步者工具包的唯一问题是,你需要每半年注册一次,以便获得新的特许文件。ispLever 起步者版本支持 Lattice 公司的 SPLD、CPLD 和 GDX 产品,但不支持它从杰尔系统公司买来、并经内部开发的 FPGA 器件。要支持这些FPGA器件,你必须升级到售价为 495 美元的 ispLever Base 或价格更贵的升级产品。ispLever 起步者工具包中包含的设计输入选件有 Verilog、VHDL 和原理图,定时约束和引脚输出约束的输入,Mentor Graphics 公司和 Synplicity 公司开发的综合引擎,Lattice 公司开发的 ispVM 可编程实用程序,以及进行功能模拟和时序模拟的能力。

几年前作者通过使用 Cypress 公司的包含 Verilog 和 VHDL 的 Warp 工具集学会了 VHDL(参考文献 5)。售价为99美元的Warp 包括内容广泛的《面向可编程逻辑的 VHDL》参考手册。Warp 支持 Windows 和 Unix 操作系统,而且它的有限状态机编辑程序和定时模拟程序均出自 Aldec公司。与我们所评估过的其它工具集不同,它很容易让你在 Warp 中创建与器件和厂商无关的 HDL 设计,然后将其高效率地编译成 Cypress 公司的可编程逻辑器件。

评论