在DDR3 SDRAM存储器接口中使用调平技术

引言

本文引用地址:https://www.eepw.com.cn/article/86471.htmDDR3 SDRAM存储器体系结构提高了带宽,总线速率达到了600 Mbps至1.6 Gbps (300至800 MHz),它采用1.5V工作,降低了功耗,90-nm工艺密度提高到2 Gbits。这一体系结构的确速率更快,容量更大,单位比特的功耗更低,但是怎样才能实现DDR3 SDRAM DIMM和FPGA的接口呢?调平技术是关键。如果FPGA I/O结构中没有直接内置调平功能,和DDR3 SDRAM DIMM的接口会非常复杂,成本也高,需要采用大量的外部元件。那么,什么是调平技术,这一技术为什么非常重要?

为提高信号完整性,实现更好的性能,JEDEC针对时钟和命令/数据总线定义了飞越(fly-by)匹配。飞越拓扑降低了同时开关噪声(SSN),但是当时钟和地址/命令通过DIMM时,每一DRAM上会出现时钟和数据/选通飞行时间(flight-time)斜移,如图1所示。

图1. DDR3 SDRAM DIMM:飞行时间斜移降低了SSN,

必须通过控制器调整数据,调整范围为2个时钟周期。

飞行时间斜移会高达0.8 tCK,增大到足以无法确定数据会对应两个时钟周期中的哪一个。因此,JEDEC针对DDR3存储器定义了“调平”功能,让控制器调整每个字节通道的时序,补偿这种斜移。

最新的FPGA具有很多特性以实现多种应用中双倍数据速率SDRAM存储器的接口,例如桌面计算机、服务器、存储器、LCD显示器、网络和通信设备等。然而,如果要使用最新的DRAM技术——DDR3 SDRAM,则需要可靠的调平方案。

FPGA I/O结构

FPGA,例如最近发布的Altera®Stratix®III器件系列,具有高速I/O,能够灵活地支持现有以及新兴的外部存储器标准。

读调平

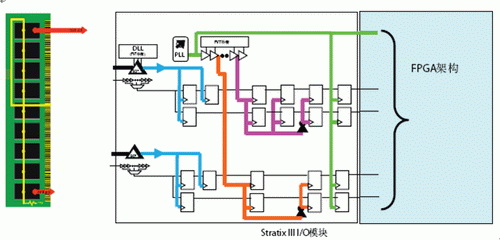

在读操作期间,存储器控制器侧必须补偿由飞越存储器拓扑引入的延时,这种延时对读周期会有影响。在数据通路上,调平不仅仅是处理I/O延时。还需要1T和下降沿寄存器来调平或者对齐所有的数据。每一DQS需要单独的重新同步时钟位置相移(PVT补偿)。图2所示为同一读命令从DIMM返回的两个DQS组。

图2. Stratix III I/O单元中的1T、下降沿和调平寄存器

开始时,每一DQS相移90度,采集组中相关的DQ数据。然后,采用自由运行的重新同步时钟(与DQS相同的频率和相位),将数据从采集域移到调平电路中——图2中以粉色和桔色链路表示。在这一阶段,每一DQS组都有独立的重新同步时钟。

下一步,DQ数据被传送至1T寄存器。在图2所示的例子中,上层通道需要1T寄存器来延时某一DQS组中的DQ数据位。请注意,在这个例子中,下层通道并不需要1T寄存器。这一过程开始对齐上层通道和下层通道。在免费的PHY IP内核校准方案中,会自动确定某些通道是否需要1T寄存器。

然后将两个DQS组传送至下降沿寄存器。如果需要,自动校准过程启动时接入或者断开可选寄存器。最后一步是将上层和下层通道对齐同一重新同步时钟,建立源同步接口,将完全对齐,即调平后的单倍数据速率(SDR)数据传送给FPGA架构。

写调平

和读调平相似,但过程相反,在单独的时间启动DQS组,对齐到达DIMM器件的时钟,必须达到tDQSS参数的+/- 0.25 tCK。

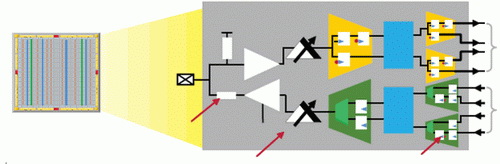

其他FPGA I/O创新

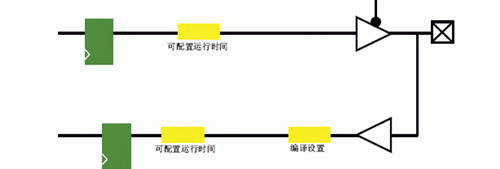

高端FPGA有很多创新的I/O特性,实现多种存储器简单可靠的接口,例如动态片内匹配(OCT)、可变I/O延时以及半数据速率(HDR)等,如图3所示。本文在下面列出这些特性(从左到右),对每一特性进行详细介绍。

图3. 适用于DDR3 SDRAM存储器接口的I/O特性

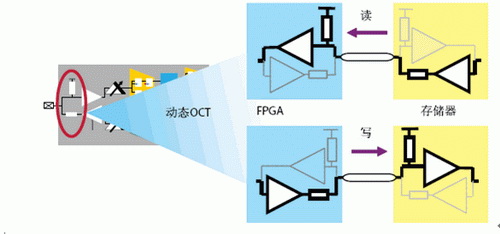

动态OCT

并行和串行OCT为读写总线提供合适的线路终端和阻抗匹配。这样,FPGA不需要外部电阻,节省了外部元件成本,减小了电路板面积,降低了走线复杂度。由于并行匹配有效地减少了写操作电流,因此,大大降低了功耗。图4所示为读写操作的终端匹配。

图4. 动态OCT – 读写操作

可变延时,实现DQ去斜移

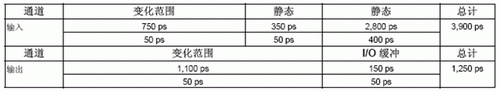

在走线长度失配和电去斜移上采用可变输入和输出延时(图5所示)。精细的输入和输出延时分辨率(即,50微微秒(ps)步长)可实现更精确的内部DQS去斜移(和调平功能分开),这一斜移是由电路板长度失配或者FPGA和存储器I/O缓冲变化引起的,如表1所示。最终,这提高了每一DQS组的采集余量。

图5. I/O单元中的静态和动态延时

表1. FPGA I/O延时

可控硅相关文章:可控硅工作原理

比较器相关文章:比较器工作原理

存储器相关文章:存储器原理

评论