双内核处理器胜任未来网络计算

——

双内核处理器胜任未来网络计算

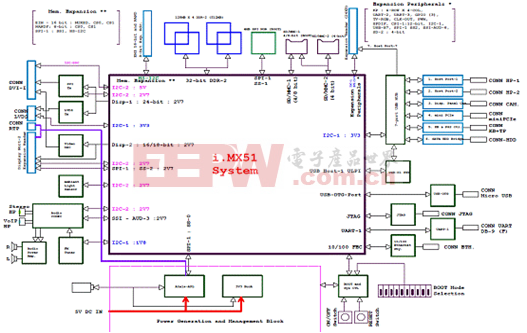

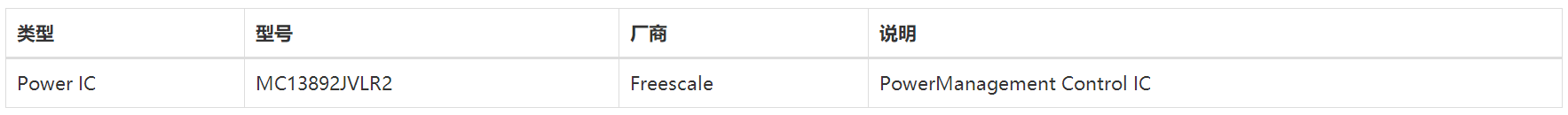

市场对于未来网络处理器的要求已经越来越清晰:在可接受的成本与功耗基础上实现更高的计算性能。飞思卡尔公司(Freescale)对此的解决方案是:开发一种内含双处理器内核的网络处理器MPDC8641D。该器件中采用90纳米SOI工艺制造,集成了两个基于32位PowerPC处理器架构的e600内核,单一e600内核的性能可达到1.5GHz,飞思卡尔预计这种双核结构将使最终的网络处理器性能加倍。

双核结构与传统的单核结构相比,优势是显而易见的。首先,双内核处理器从芯片硅成本来讲虽然比单核处理器高,但由于其可取代两颗独立单核处理器和一颗系统控制器芯片,因此可简化PCB电路的设计,有效节省应用系统的成本。其次,与通过两个单内核处理器协同工作完成的性能提升解决方案相比,单芯片内部的双内核之间可以通过高速内部总线实现更大的带宽通信,从而避免了芯片外部互连的低速PCI总线成为性能瓶颈。MPDC8641D中采用了MPX总线,其最高带宽达667MHz,可使内核间的通信延迟降到最低限度。第三,由于集成了双内存控制器,MPDC8641D中存储器带宽得到了扩展,并降低了延迟。此外,双内核架构还可使两个内核保持高度的缓存一致性,因为某一内核可将其缓存中的最新数据直接快速拷贝到另一内核中,而无需通过存储器。根据Freecale提供的数据,MPDC8641D的功率在15W~25W之间。

与这种突出的计算性能相匹配,MPDC8641D选择了RapidIO串行线路接口作为外部系统互连接口,以实现其与周边设备之间的高速互连。同时,MPC8641D处理器还内嵌了四个以太网MAC控制器,支持10/100Mbps及千兆以太网,可对通过以太网(包括IPv4、IPv6、TCP、UDP以及VLAN)传播的协议的识别和检索进行加速。此外,它还支持原有的外围与主机设备之间通过PCI Express接口的连接。

这种双核结构实际上还可以带来设计开发上的灵活性。比如,在低带宽应用中,系统开发商可以利用MPC8641D的某一个内核来管理数据面处理,而用另一个内核管理控制面;或者用一个内核管理数据面的信号发射,而另一个内核管理信号接收;在高带宽应用中,两个内核都可与一颗网络处理器或ASIC配合工作,其中一个内核卸载任务,如分类、安全和高质量。开发商还可选择让双内核使用同一操作系统,从而简化到现有系统升级到采用双内核系统的软件移植。目前已经有Enea Embedded Technology、Green Hills Software、Metrowerks、QNX、Wind River等开发商表示会为这款网络处理器提供软件或开发工具支持。

双核结构与传统的单核结构相比,优势是显而易见的。首先,双内核处理器从芯片硅成本来讲虽然比单核处理器高,但由于其可取代两颗独立单核处理器和一颗系统控制器芯片,因此可简化PCB电路的设计,有效节省应用系统的成本。其次,与通过两个单内核处理器协同工作完成的性能提升解决方案相比,单芯片内部的双内核之间可以通过高速内部总线实现更大的带宽通信,从而避免了芯片外部互连的低速PCI总线成为性能瓶颈。MPDC8641D中采用了MPX总线,其最高带宽达667MHz,可使内核间的通信延迟降到最低限度。第三,由于集成了双内存控制器,MPDC8641D中存储器带宽得到了扩展,并降低了延迟。此外,双内核架构还可使两个内核保持高度的缓存一致性,因为某一内核可将其缓存中的最新数据直接快速拷贝到另一内核中,而无需通过存储器。根据Freecale提供的数据,MPDC8641D的功率在15W~25W之间。

与这种突出的计算性能相匹配,MPDC8641D选择了RapidIO串行线路接口作为外部系统互连接口,以实现其与周边设备之间的高速互连。同时,MPC8641D处理器还内嵌了四个以太网MAC控制器,支持10/100Mbps及千兆以太网,可对通过以太网(包括IPv4、IPv6、TCP、UDP以及VLAN)传播的协议的识别和检索进行加速。此外,它还支持原有的外围与主机设备之间通过PCI Express接口的连接。

这种双核结构实际上还可以带来设计开发上的灵活性。比如,在低带宽应用中,系统开发商可以利用MPC8641D的某一个内核来管理数据面处理,而用另一个内核管理控制面;或者用一个内核管理数据面的信号发射,而另一个内核管理信号接收;在高带宽应用中,两个内核都可与一颗网络处理器或ASIC配合工作,其中一个内核卸载任务,如分类、安全和高质量。开发商还可选择让双内核使用同一操作系统,从而简化到现有系统升级到采用双内核系统的软件移植。目前已经有Enea Embedded Technology、Green Hills Software、Metrowerks、QNX、Wind River等开发商表示会为这款网络处理器提供软件或开发工具支持。

评论