边界扫描测试技术(04-100)

——

支持器件

本文引用地址:http://www.eepw.com.cn/article/81044.htm对边界扫描系统级测试能力的需求增加,促进开发各种支持器件,如3和4端口网关,扫描通路线路和多扫描端口。

根据设计结构要求,可得到封装类型、大小和工作电压不同的器件。一些供应商也提供象IP那样的器件功能,可用CPLD、FPGA或ASIC器件嵌入IP。

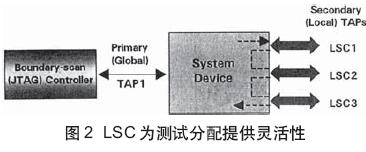

这些器件的重要功能是提供从主边界扫描总线到特定本地扫描链(LSL)的接入,这如同系统级器件协议选择那样。扫描链不是单独选择就是任意组合中的菊花链,这为测试分配提供了灵活性(见图2)。

这对于支持闪存器件系统内编程而分配板设计是有用的。在这些环境下,在板上围绕边界扫描移位的向量数应该保持绝对最少,以使闪存编程周期时间最佳。

闪存编程

理想情况,对于闪存而言,具有对闪存地址、数据和控制信号网直接接入的边界扫描器件可放置在单个LSC上。此LSC只在闪存编程相被选择。换句话说,为执行板级内连测试选择所有LSC或为执行功能逻辑组测试可选择专门的LSC。在此,假设用外部边界扫描控制器驱动测试图形或向量,通过总体扫描链基础结构到各个板。

一些嵌入式控制结构通常在IEE1149.1系统测试配置中实现,在嵌入式边界扫描控制器件的控制下,这种结构将允许测试向量的时序,测试向量一般存储在闪存中。

嵌入式控制器可按排在单系统主机板上或安排在系统环境中的多板上,它支持嵌入向量输送方法。这最普通的是系统总线主机结构。

系统测试总线主机

在此,背板中的一个模件是系统主机,而其他模件变成从机(见图3)。用于测试从模件或多板中执行测试的边界扫描向量安排在系统主机板上的闪存中。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论