灵活的动态电源管理解决方案

嵌入式系统产品的主要差别是其电源效率,因为较低的功率导致低运作成本、低扇出噪声和低冷却要求。因此,现代嵌入式系统着重于增强系统功能,同时降低运行功耗、增高工作频率,或者采用更强大、更高密度的VLSI集成电路以提高系统的性能,但是又不可避免地增加了功耗。减少系统级功耗的一种方法是使用低静态功耗的器件。此外,在系统运行期间的功耗主要取决于所处理的负载。这种方法称为动态电源管理。

本文引用地址:https://www.eepw.com.cn/article/78390.htm基于CMOS技术的数字系统中,下面的数学方程描述了功耗、工作频率和电压之间的关系。

系统功耗= aC×V2×F

方程中C是信号传输时所有电路中需要充电的总电容。V是加至器件的电压,F是信号切换频率。从方程中可知,降低电压或频率,或者同时降低两者,能够降低整个系统的功耗,这是动态功率管理的基本原理。动态功率管理鉴别低处理要求时段,降低工作电压和频率,这样就能减少平均运作功耗。此外,在空闲时段,关闭电路板上某些电路的电源可以进一步减少功耗。

系统运行期间,由软件来决定电压或者频率的减少量。本文阐述了作为这一电源管理软件的外设工作的电路。

动态电源管理方法的几个问题

设计一个具有动态电源管理能力的系统时,设计者应该认识到下列问题:

1.工作电压与频率的执行时间。

电源需要一定的时间上升到新的工作电压,这个延时通常是电源总线上负载的函数。对于时钟发生器来说,频率之间变化所要求的时间可以是很短暂的。因此,操作系统必须监控工作电压以及决定什么时候改变频率。

2. 电压或频率的转变期间处理器或许不能可靠工作。

电源电压或输入时钟频率改变时,许多能够工作在不同的电压和相应频率的CPU也许不能可靠地工作。在这种情况下,建议在电压或频率的转变时,暂停CPU的工作。这就要求外部的硬件电路监控电压和频率,阻止CPU在转变期继续工作。

3. CPU与集成的PLL通常产生集成的外围设备产生所需要的频率,也为外部总线接口提供时钟。倘若CPU时钟频率改变,PLL必须重新编程以维持外围设备的工作频率,这些外围设备并未设计成工作于不同的频率。含有片内PLL的CPU会使频率范围受到限制。一个外部的PLL能容易地克服这个限制,扩展节约功率的范围同时又能满足电路板上使用的其它外围设备的时钟要求。

动态电源管理实现的原理

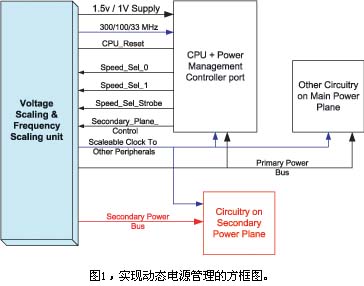

电路板上实现功率管理功能的框图如图1所示。用软件来实现电源管理算法,用硬件来定标电压和频率,以此共同控制整个电路板的功耗。

1.控制CPU和电路板上其它电路的工作频率;

2. 控制CPU的内部电压;

3. 空闲期间关闭第二组电源;

在图1的左面,电压标定和频率标定单元接受来自电源管理端口的命令并产生要求的内部电压、CPU时钟频率以及关闭或开启第二组电源总线。电源管理信号如下:

Speed_Sel_0 Speed_Sel_1 命令信号译码为

00 全功率 CPU电压=1.5V,工作频率=300MHz

01 中等功率 CPU电压=1.0V,工作频率=100MHz

10 低功率 CPU电压=1.0V,工作频率=30MHz

11 用这个信号控制第二组电源 0 关闭第二组电源;1开启第二组电源

Speed_Sel_Strobe 锁存来自电源管理控制器端口的命令,电路板上其余的电路分为主电源电路和第二组电源电路。

莱迪思公司的ispPAC Power Manager 和 ispClock5520能非常方便地实现宽范围的动态电源管理功能。

ispClock5500特性

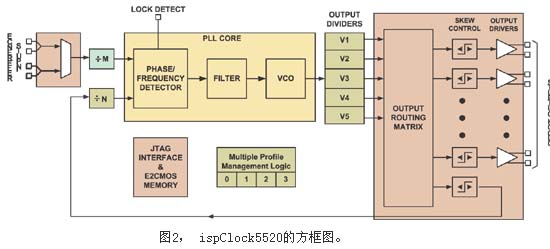

ispClock5500系列有两个器件,10个输出的ispClock5510和20个输出的ispClock5520。它们可以构成灵活的高性能时钟产生器,具有通用扇出缓冲器。时钟产生器能提供多达5个时钟频率,从10MHz到320MHz,采用高性能的PLL和时钟倍频,分频功能。通用扇出缓冲器能驱动使用单端或者差分的20个时钟网络,且有独立的用于改进信号与时序完整性的输出控制功能。这些新器件有着优越的性能和灵活性,支持电路板上的高性能时钟网络设计。

可编程 I/O:输入部分为两个硬件可选的多路时钟输入。输出部分为多达20个低扭曲时钟输出。参考时钟输入和时钟输出可以分别编程,然后与单端逻辑(LVTTL LVCMOS SSTL HSTL)和差分逻辑(LVDS LVPECL Differential HSTL Differential SSTL)相接口。输入和输出终端电阻可编程范围在40Ω~70Ω,以每5Ω为一档。每个时钟输出的输出扭曲可以独立地设置成16档中的一种,分辨率为195ps。扭曲的间隔大小源自PLL频率,因此是非常精确的。频率综合单元能够产生多达5个时钟频率。无阻塞的输出转换阵列可以把任意频率送至任意输出。输入频率范围从10MHz到320MHz,输出频率从5MHz到320MHz。

PLL核:器件的核心是高性能PLL核,由相位频率检测器(PFD),可编程片上滤波器和VCO组成。PLL核能锁存的输入频率范围是10MHz到320MHz,而输出频率范围在320至640MHz,输出抖动小于100ps。

频率综合分频器:器件有7个5位计数器:M,N和5个V计数器。M,N和一个V计数器有5位分辨率用于设置PLL的工作频率。PLL的输出驱动其余的V分频器,只与PLL工作频率相关的5个独立频率得到了综合。

JTAG编程和扫描接口:器件使用JTAG接口编程,也可以用标准的在线检测器检测电路板的互联关系。

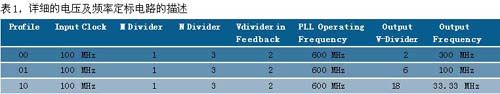

时钟管理模式:器件能存储4个独立的配置(M、N、V计数器和扭曲),能选择4组独立的时钟频率。电路的频率定标使用了ispClock的管理模式特性,为CPU提供3个时钟频率,300MHz、100MHz和33MHz。其余的输出可以通过编程提供3个时钟频率的4组,使用其余的V计数器,这些时钟与CPU的时钟不同,所有的功能均通过相同的选择引脚来控制。此外,设计使用ispClock的同步选通信号(Sync_gate),用以防止畸形的时钟周期。下列表格列出了不同的管理模式对应的各种配置值。

设计实例:Power

1208p1+ispclock5520方案

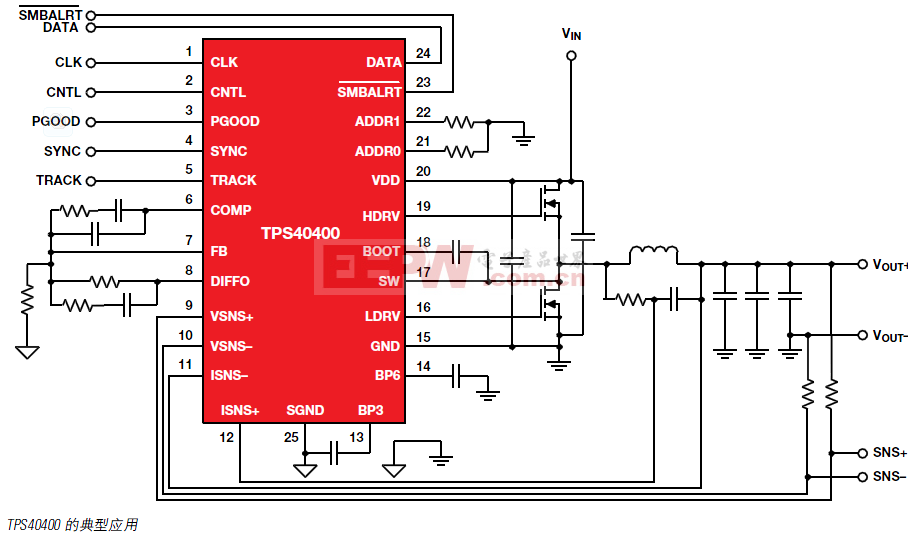

图3为Power1208P1(ispPAC-POWR1208P1),器件提供所有的逻辑功能,用于电压和频率的定标功能。此外还驱动ispClock5520。考虑到电压和频率的转变时间,它遵循来自电源管理端口的命令,独立地控制第二组电源。ispClock5520产生所要求频率定标的各种时钟频率。总共有20个时钟输出,通过编程产生用于电路板各部分的不同时钟频率。

Power1208P1的功能包括:寄存与执行来自电源管理控制端口的命令;控制B1电压在1.0V和1.5V之间变换;监控所有电源电压;产生用于ispClock至输出频率之间转换的控制信号;开启跟踪主电源总线;控制跟踪第二组电源总线;上电时脉冲展宽CPU复位信号,电源发生故障时激活CPU复位信号。

ispClock的4种模式中的3种可以配置产生不同的时钟频率,这里只讨论CPU频率的改变,同样的机理可用于所有时钟输出。

电源B1的电路运作:通过调整引脚和输出电压引脚之间连接电阻R1和R2,图3中顶部左面的电源B1的输出电压可设置成1.5V。如果只把R1连接在输出和调整输入之间,输出电压为1.0V。MOSFET Q1开启时,将电阻R2短路。结果B1的输出电压变为1.0V。然而,Q1关闭时,B1的输出电压成为1.5V。驱动MOSFET Q1,控制HVOUT引脚斜率,在电压从1.0V变至1.5V或者从1.5V变至1.0V时,限制电流涌入。

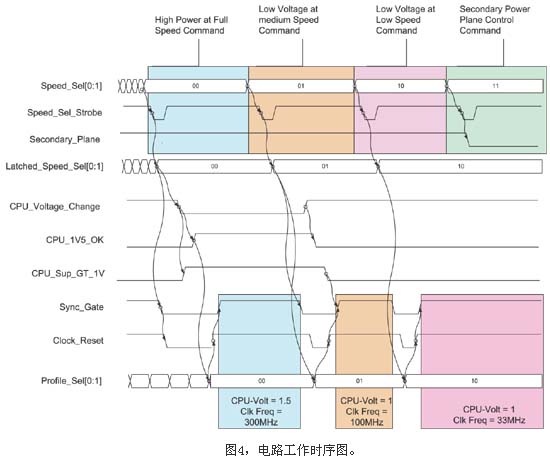

图4为上述电路工作的时序图。图的顶端是来自电源管理控制端口的命令。Power1208P1和ispClock5520执行命令。电源电压和时钟频率到达稳态后,这个稳态是稳定的。

上述设计在最小的电路板面积上提供了最大的灵活性。IspClock5520对时钟频率定标功能是理想的,因为它可以取代4个独立的时钟产生器件和与之相关的从多路时钟缓冲器中选出一路时钟的价格昂贵的逻辑电路。

用于这个设计的Power1208P1器件不但有电源电压还有监控逻辑信号的能力。此器件的逻辑部分能在控制电源电压和监控CPU电压轨迹的同时,方便地集成所有的逻辑功能,能可靠地在不同的工作速度之间进行转换。其结果是设计能够在配置之间安全地转换。

电源滤波器相关文章:电源滤波器原理

负离子发生器相关文章:负离子发生器原理 分频器相关文章:分频器原理 尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论