可扩展多核嵌入式处理器优势凸现

在2007年第十二届国际集成电路展上,首次进入中国市场的IntellaSys公司带来了他们极具挑战性的最新成果——可扩展多核嵌入式处理器以及用于下一代消费电子产品的“三重播放”芯片解决方案。

本文引用地址:https://www.eepw.com.cn/article/78359.htm

IntellaSys公司亚太区销售副总裁王彦之介绍说,近年来的发展趋势是把一个甚至两个DSP核和高速乘法器/累加器电路结合起来,跟上多媒体的速度。但是,由于增加更高位流的速度要求看来是无止境的,这种方法很有可能要达到它的极限。一个更好的方法是把几个处理器核集成到芯片上,每一个都比复杂的DSP核简单,但是每一个处理器核都有一个高速乘法器/累加器。这些处理器核如果妥善设计,就可以把计算任务分配给各个处理器核共同进行,从而能够执行复杂的算法。当然这要重新写入算法,以便把计算任务分解,由多个处理器核分担,结果可能令人难以置信地提高了处理器的能力。例如,可以让1个处理器核去管理外接存储器,让8个处理器核负责快速富利叶变换,完成多媒体算法,再让几个处理器核带动应用系统中各种I/O子系统。这与使用单个处理器处理多任务的传统方法是完全不一样。例如,MP3的音频处理可用8个处理器内核实现、而H.264的编解码则需要16个处理器内核。

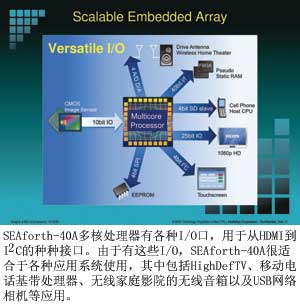

王彦之说,公司此次展示的将声音、数据、图像“三重播放”芯片解决方案中就采用了拥有40个18位处理器内核的SEAforth多核处理器。SEAforth-40多核处理器将4个A/D和4个D/A转换器和布置成10×4(40个)处理器核组合在一起,每个处理器的处理速度是每秒执行10亿条指令,每个处理器核含有128个字节RAM和128个字节ROM,2个SPI I/O口,25位通用并行I/O和8位SD从端口,而一个典型应用系统的全部功耗只有250mW。王彦之表示,SEAforth多核处理器提供的是一种可扩展的解决方案,由于应用软件位于处理器核之外,当发生某些改变时只需修改应用软件,因此可以缩短产品面市时间,降低客户成本。目前公司已推出了24核、40核的产品,计划将在明年推出一款多达100个~120个内核的嵌入式处理器产品。

随着越来越多嵌入式处理器芯片应用在移动应用系统中,对低功耗的要求越来越重要。但对多核芯片能够按照数据是否出现来启动处理器核或者让它停下来,因此节电的办法要简单得多。王彦之介绍,在多核处理器中各个处理器核之间的数据通路是自动同步的,完全没有必要对处理器本身进行同步。这就是说,不需要一个中央时钟为每个处理器核提供时钟信号。没有了中央时钟,也就意味着可减少几百万个晶体管随时钟信号的每一次嘀嗒一声而消耗功率。多核处理器中,每个处理器核各有一个时钟(一个简单的环形振荡器),它的速度和硅半导体的速度一样快。根据经验,我们估计,在任一时刻,只有三分之一的处理器核在工作,过几纳秒后,另外一组处理器核接通电源。但仍然大约只有三分之一的处理器核在工作。这样就能有效地降低整个芯片的功耗,约降低了三分之二,从而进一步提高了整个系统的性能。

评论