常用的电平转换方案

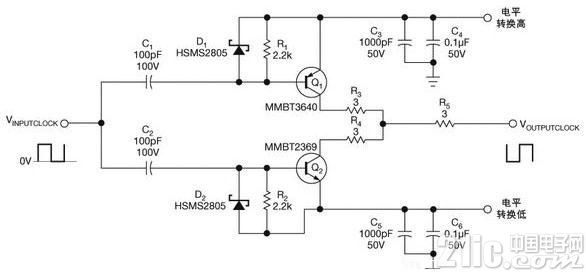

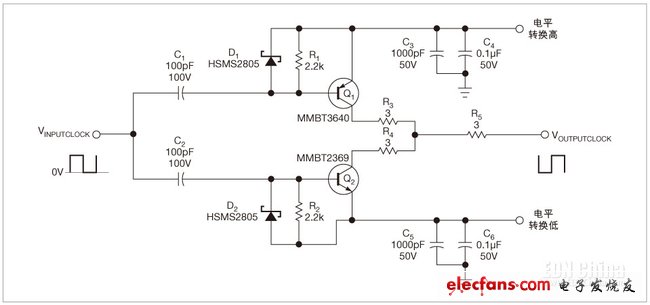

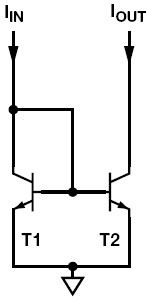

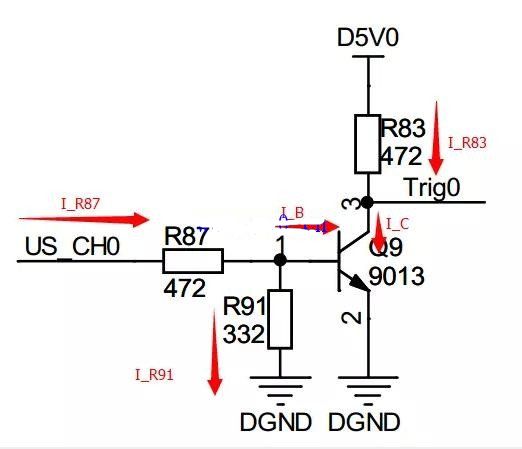

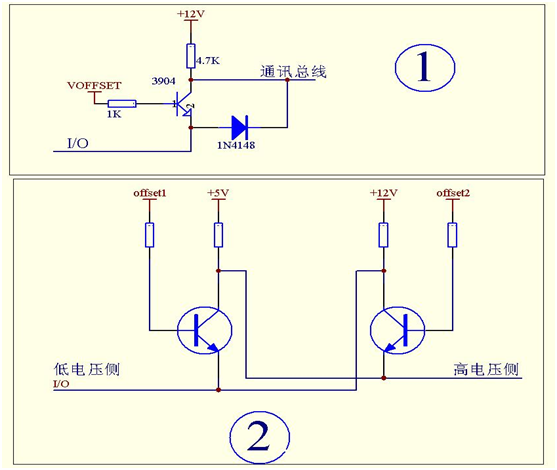

就是一个双极型三极管或 MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。

(2) OC/OD 器件+上拉电阻法

跟 1) 类似。适用于器件输出刚好为 OC/OD 的场合。

(3) 74xHCT系列芯片升压 (3.3V→5V)

凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作 3.3V→5V 电平转换。

——这是由于 3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而 CMOS 的输出电平总是接近电源电平的。

廉价的选择如 74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列 (那个字母 T 就表示 TTL 兼容)。

(4) 超限输入降压法 (5V→3.3V, 3.3V→1.8V, ...)

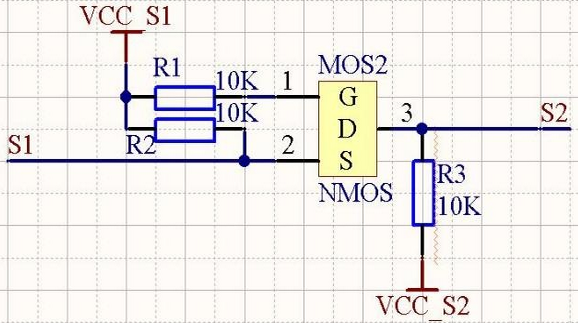

凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。

这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制 (改变了输入级保护电路)。

例如,74AHC/VHC 系列芯片,其 datasheets 明确注明"输入电压范围为0~5.5V",如果采用 3.3V 供电,就可以实现 5V→3.3V 电平转换。

(5) 专用电平转换芯片

最著名的就是 164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的 (俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。

(6) 电阻分压法

最简单的降低电平的方法。5V电平,经1.6k+3.3k电阻分压,就是3.3V。

(7) 限流电阻法

如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如 74HC 系列为 20mA),仍然是安全的。

(8) 无为而无不为法

只要掌握了电平兼容的规律。某些场合,根本就不需要特别的转换。例如,电路中用到了某种 5V 逻辑器件,其输入是 3.3V 电平,只要在选择器件时选择输入为 TTL 兼容的,就不需要任何转换,这相当于隐含适用了方法3)。

(9) 比较器法

算是凑数,有人提出用这个而已,还有什么运放法就太恶搞了。

2. 电平转换的"五要素"

(1) 电平兼容

解决电平转换问题,最根本的就是要解决逻辑器件接口的电平兼容问题。而电平兼容原则就两条:

VOH > VIH

VOL < VIL

再简单不过了!当然,考虑抗干扰能力,还必须有一定的噪声容限:

|VOH-VIH| > VN+

|VOL-VIL| > VN-

其中,VN+和VN-表示正负噪声容限。

只要掌握这个原则,熟悉各类器件的输入输出特性,可以很自然地找到合理方案,如前面的方案(3)(4)都是正确利用器件输入特性的例子。

(2) 电源次序

多电源系统必须注意的问题。某些器件不允许输入电平超过电源,如果没有电源时就加上输入,很可能损坏芯片。这种场合性能最好的办法可能就是方案(5)——164245。如果速度允许,方案(1)(7)也可以考虑。

(3) 速度/频率

某些转换方式影响工作速度,所以必须注意。像方案(1)(2)(6)(7),由于电阻的存在,通过电阻给负载电容充电,必然会影响信号跳沿速度。为了提高速度,就必须减小电阻,这又会造成功耗上升。这种场合方案(3)(4)是比较理想的。

(4) 输出驱动能力

如果需要一定的电流驱动能力,方案(1)(2)(6)(7)就都成问题了。这一条跟上一条其实是一致的,因为速度问题的关键就是对负载电容的充电能力。

(5) 路数

某些方案元器件较多,或者布线不方便,路数多了就成问题了。例如总线地址和数据的转换,显然应该用方案(3)(4),采用总线缓冲器芯片(245,541,16245...),或者用方案(5)。

(6) 成本&供货

前面说的164245就存在这个问题。"五要素"冒出第6个,因为这是非技术因素,而且太根本了,以至于可以忽略

评论