Altera Stratix 10 DRAM SIP突破带宽瓶颈

计划于2017年出货的最新的Stratix 10 DRAM SiP产品将采用存储器厂商现代公司的HBM DRAM内存,通过英特尔先进的嵌入式多裸片互连桥接(EMIB)技术,将FPGA、MCU、DSP以及DRAM等其他功能模块集成在2.5D的SiP封装内,实现一个异构多核的SoC FPGA产品。相对于目前的分立DRAM解决方案,Stratix 10 DRAM SiP的存储器带宽提高了10倍。

本文引用地址:https://www.eepw.com.cn/article/283392.htm伴随着客户对系统的要求不断攀升,处理器芯片的技术不断地提升性能,随着技术难度增加,发展将越来越慢。而FPGA方面,还有EMIB的技术、存储技术等,不管是DDR3、DDR4,它们已经不再能够跟上客户对系统的要求了,所以关键就是在存储器带宽上。但存储器子系统所提供的带宽与系统要求的存储器带宽差距越来越大。

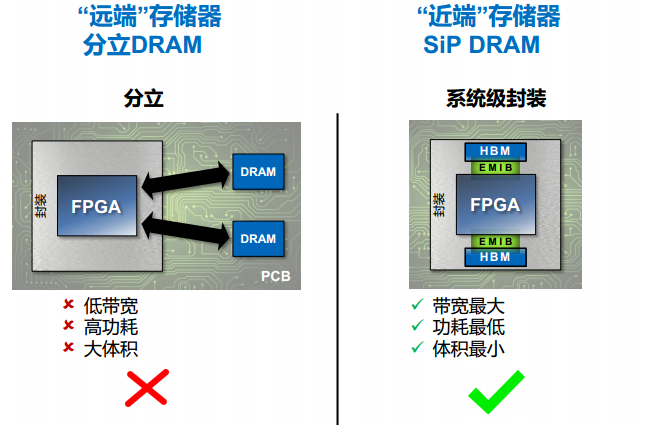

如图1所示,传统的“远端”存储器分立DRAM由于其低带宽、高功耗、大体积不能满足下一代应用的需求。Altera Stratix 10 DRAM SIP 产品本身的电路板它的尺寸变小,DRAM器件直接被集成到了FPGA的器件里面,因此就出现了所谓原来的传统的远端的存储器变成了近端的存储器。这样做有三大优势,第一可以实现最大的带宽,10倍于以前的带宽;第二体积最小,可以把更多的管芯放到一个单一的封装中;第三它的功耗可以实现最低。 图1 DRAM SIP与传统DRAM 对比

据了解,Stratix 10系列面向的包括数据中心、HPC、雷达、定制服务器等高端市场。通过英特尔独有的EMIB技术实现,相对于现在流行的TSV技术连起来的话,在信号的完整性和性能、功耗等方面都具有优势。

Altera公司高级产品营销总监 Manish Deo对此解释道:“EMIB的技术其实强调是系统级的这样一个互联集成的技术,当你需要把FPGA和外部世界,其实就是外部器件系统相连的时候,任何一个技术厂商都是要尽量多地避免使用TSV,因为如果你要用TSV连接的话,意味着你的信号,也就是数据要不断地推动TSV进出,而事实上我们任何一个系统,尤其是高处理的这些系统解决方案都有大量的数据的进出,所以吞吐量是非常之大的,EMIB的好处就是当FPGA和外界系统相连接的时候,它可以完全绕过TSV,不再需要通过TSV去访问存储器。所以这是EMIB的技术和任何其他的基于中介质集成的解决方案根本上的不同。”

Altera公司产品营销资深总监Patrick Dorsey在其最新产品Stratix 10 DRAM SiP的发布会表示:“SoC FPGA已经进入4核乃至16核时代,集成有500多万个逻辑单元,DSP的浮点运算能力达到10T FLOPS,面临的一个关键的问题是这些数据如何快速传输到核心处理单元, 因此存储器的访问越显重要。

评论