恒比定时器具体实现电路解析

之前分别介绍了什么是CFD电路,CFD电路实现原理框图;以及CFD电路在整个PET系统中地位。毋庸置疑,CFD已成为PET系统中非常重要的功能模块,经理十几二十年的发展,其实现方法并未有突破性的改变,然而这对于工程应用或者是要学习掌握这项技术的工程师来说并非坏事,掌握了基本原理,万变不离其宗。

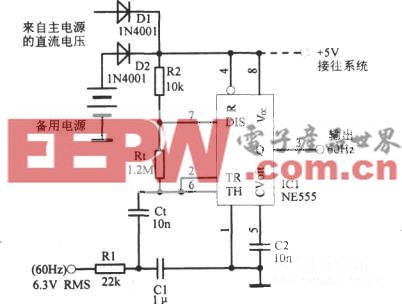

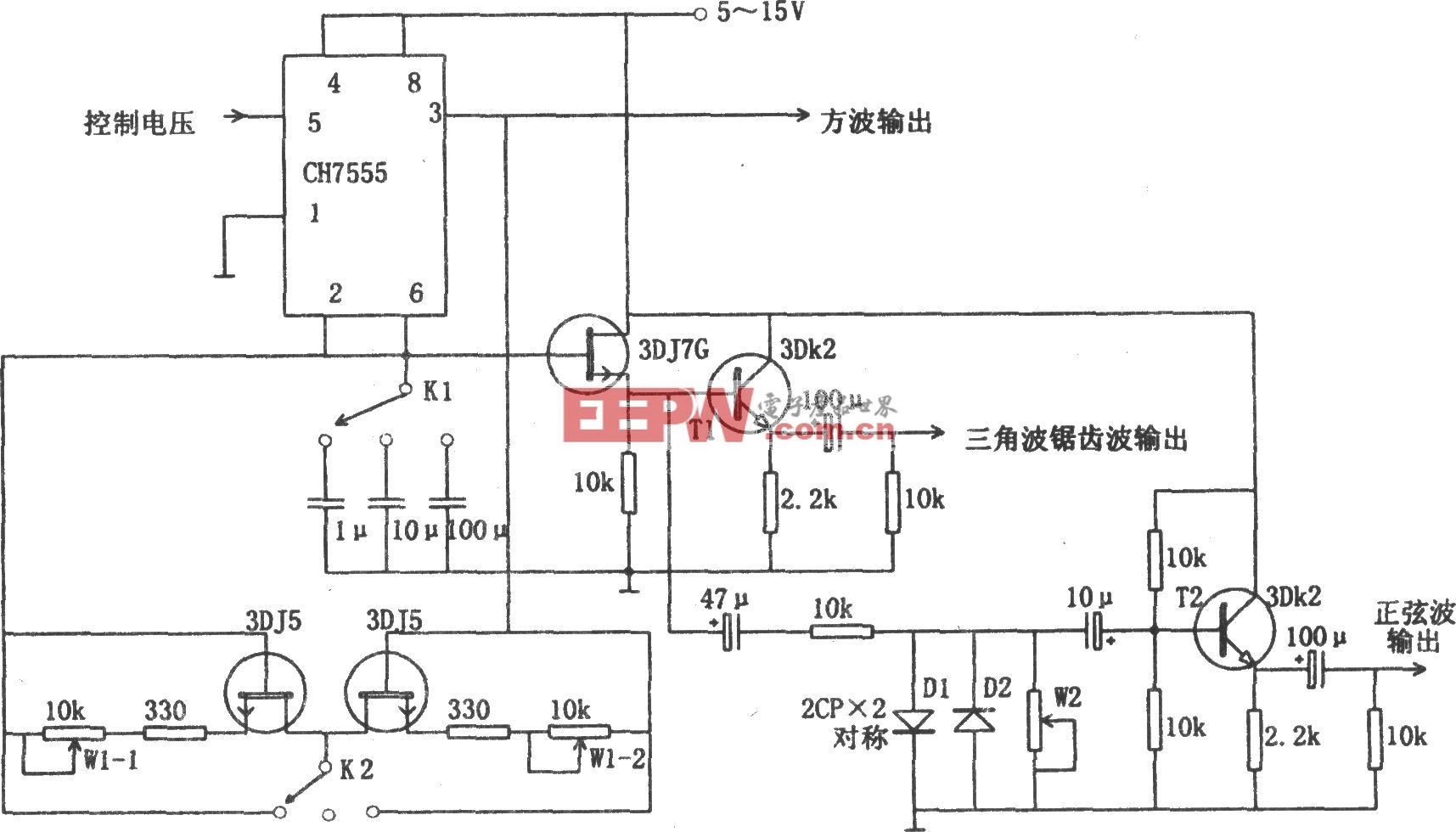

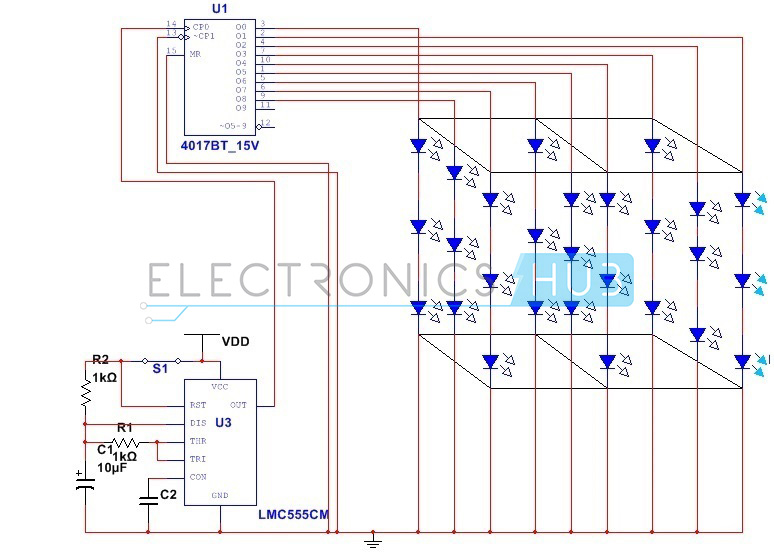

本文引用地址:https://www.eepw.com.cn/article/282236.htm图1是参考【1】介绍的具体实现电路,下面我们先介绍这个电路,然后引出实际工作中笔者接触到的CFD电路实现方法。

图1:一种实际得到采用的CFD电路

如图1所示这个电路采用的芯片是AD96687,里面有两路比较器。实际的 CFD 电路除了恒比定时甄别电路外,还有预甄别器和输出成形电路。 比较器CP1作为预甄别器, 通过电位器 RT 1 来选择阈值,甄别掉噪声引起的触发,只有信号幅度大于V T1的信号才能触发。两个快比较器 CP1 和CP2 分别作为预甄别器和恒比定时甄别器。

整个电路的工作流程如下:幅度超过下阈值的信号通过预甄别器先使触发器FF1 的输出Q1置高,此时触发器 2 的置位端 R2 无效, D2 变为高电平;在恒比定时甄别器输出的上升沿,触发器FF2 的输出端 Q2 变高, 使FF1 置位, 触发器输出端Q 1 变为高电平, 反过来又将FF2复位,形成一个窄脉冲输出信号。

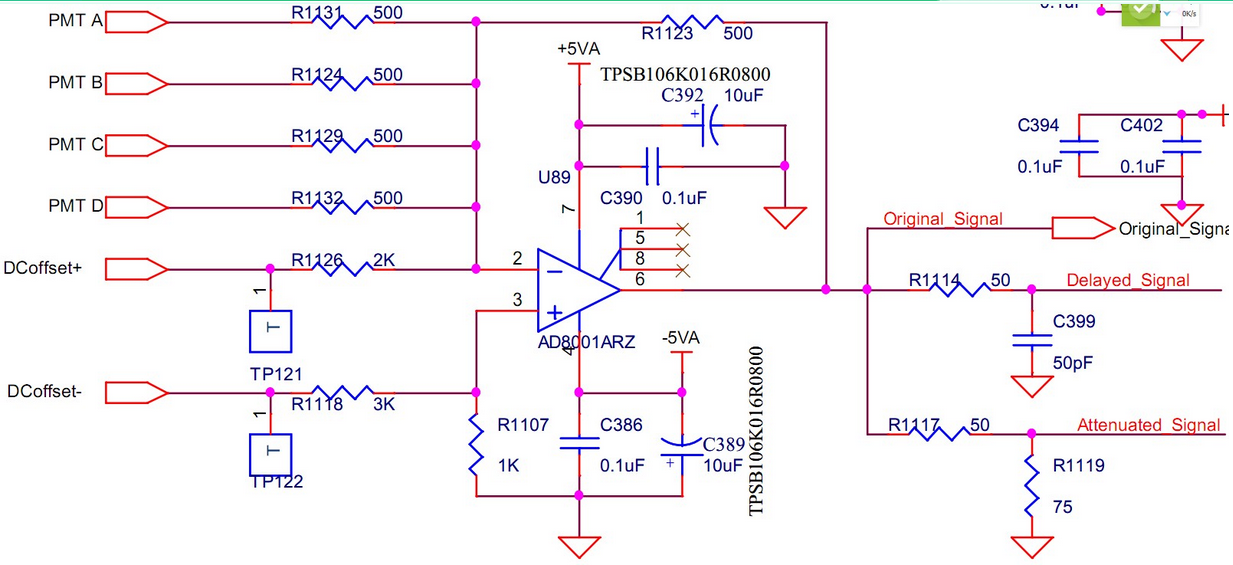

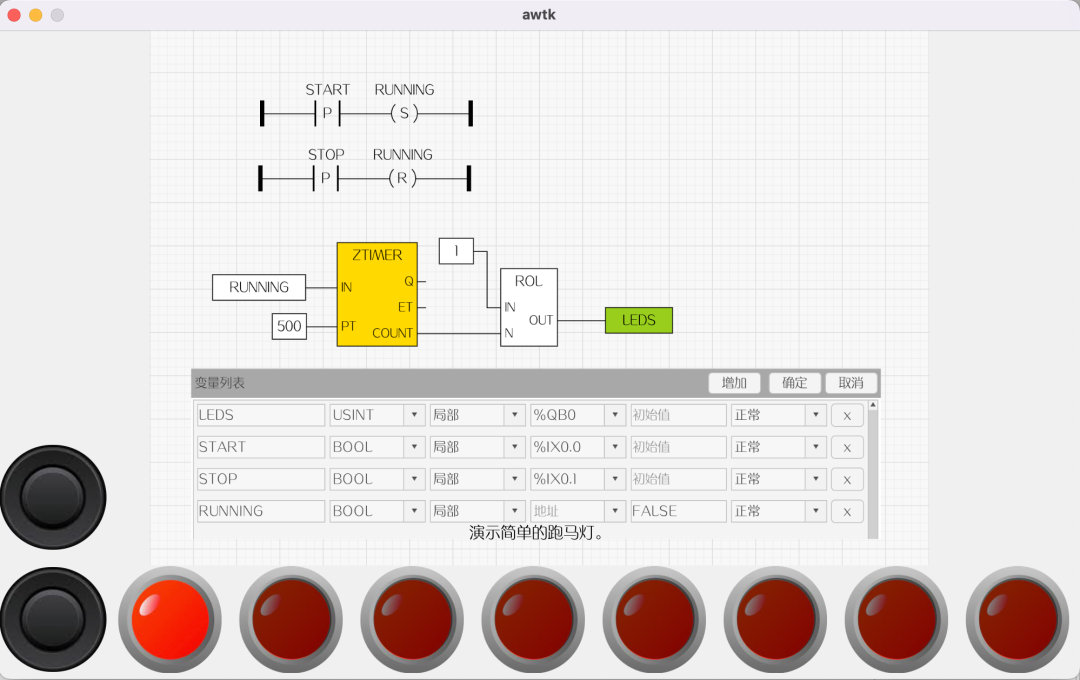

对于这个电路,笔者唯一的疑问如图1表示的文字所示,就是减法器正向输入端的输入信号如何实现对原始输入的衰减呢?我们知道根据前面博文介绍的CFD原理,放大器一路输入为原始输入的反相加延迟,另外一路则为原始输入的衰减。这里笔者没有看明白;另外还有一点是图1中输入Vi应该是四个PMT信号的整合,正如图2所示笔者所示接触到底的CFD电路那样,通过一个放大器实现加法器将四个PMT信号相加得到CFD的原始输入。

图2:CFD输入信号产生电路

图2除了展现了图1没有展现的CFD的输入Vi的产生电路,另外我们看到原始输入被分成了三路:分别是Original_signal、Delayed_signal以及Attenuated_signal,即原始输入、延迟以及衰减后的信号。

而后续CFD电路则由一款美信的双路比较器来完成,基本原理与图1类似,这里由于公司知识产权关系,就不详细剧透了。希望大家通过这几篇博文的介绍大致了解下什么是CFD,以及CFD基本原理和实现电路,也为自己学习留个记录。

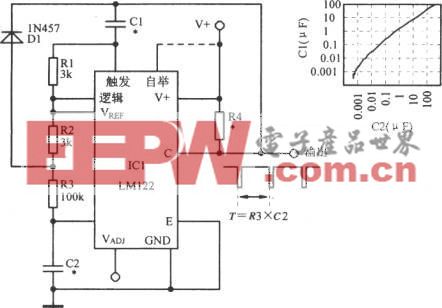

参考【1】:一种无延迟线的恒比定时器

评论