数字电路中的竞争与冒险

在了解竞争与冒险之前,先从一个很简单的电路入手。

本文引用地址:https://www.eepw.com.cn/article/270364.htm

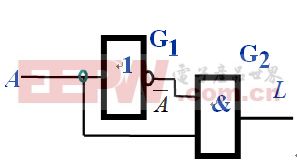

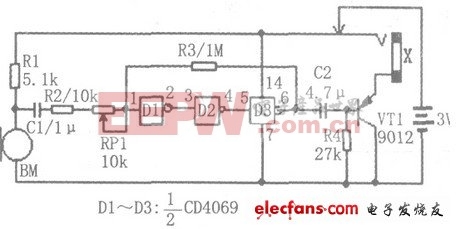

上面这个电路中,整个电路由非门G1和与门G2构成,输入输出之间不存在任何形式的反馈,亦不存在存储电路,所以这个电路是个组合逻辑电路。

输入信号为A,输出信号为L,G1门的输出为 。

每个门电路从输入激励出现到输出响应,会有一定的时间延迟,这个时间通常叫做门电路的开关延迟时间。

制造工艺、门的种类甚至制造时微小的工艺偏差,都会引起这个开关延迟时间的变化,是一个非常随机离散的常量,这里只需要知道有这么个时间差存在。

OK,回到电路中来,了解数字电路的朋友应该很快会得到输出的表达式: ,按照这个表达式,L应该输出一个恒定的低电平或者说逻辑“0”才对。

可是实际情况真的是这样吗?

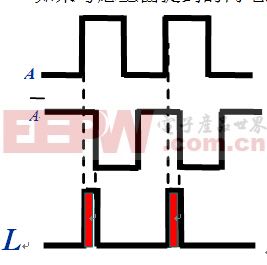

如果考虑上面提到的门电路延迟时间,可以发现,一切都变了,如下图:

信号A通过G1门,由于G1门的延迟时间的存在,会导致G1门的输出 会落后于A一个极微小的时间到达G2门的输出端,这样就导致A和 的信号波形之间有一个极小的“错位”,正是由于这个“错位”的存在,使得输出L在“错位”的瞬间输出了理论上本不应该出现的高电平(逻辑“1”),如图中虚线对应的红色电平区域。这种窄脉冲或者叫毛刺的出现,会对后级逻辑电路产生不可预计的影响,特别是在一些高速的数字电路中。

从上面的分析,不难得出结论,如果门电路的多个输入信号到达输入端的时间不同,就有可能引起输出逻辑的错乱。

为什么会到达时间不同呢?不外乎就是,不同信号通过的路径不同,相同工艺制造条件下,输入信号传输到指定输入端的传输路径上的门电路越多,需要消耗的时间也就越多,如果每个信号的路径差异都比较大,到达指定输入端的信号就会有先后,输出就有可能出现逻辑错误。当然,一些PCB走线的寄生效应也会引起这种现象,这里不讨论。

OK,把上面的思考归纳一下。

在数字电路中,信号由于经由不同路径传输达到某一汇合点的时间有先有后的现象,就称之为竞争,英文名Race;由于竞争现象所引起的电路输出发生瞬间错误的现象,就称之为冒险,英文名Hazard或者Risk。英文名字还是相对比较好理解,想象一下,两个成绩完全一样的跨栏运动员(racer),同时跑110米栏,一个跑11个栏,一个跑20个栏,最后肯定不会同时到达终点;而Hazard或者Risk,则指未来可能存在的危机和风险。不得不感慨,有些东西,还是看鸟文比较好理解。

但是需要注意的是,竞争和冒险之间的关系。有竞争不一定有冒险,但出现了冒险就一定存在竞争。如果信号的传输途径不同,或各信号延时时间的差异,信号变化的互补性等原因都很容易产生冒险现象。

该如何规避这种竞争与冒险所带来的电路设计失败风险呢?下次再聊。

电路相关文章:电路分析基础

数字滤波器相关文章:数字滤波器原理

评论