FPGA设计开发软件ISE使用技巧之:典型实例-ChipScope功能演示

(5)选择语言类型和综合工具。

本文引用地址:http://www.eepw.com.cn/article/269339.htm如图6.63所示,本实例中设置语言类型为Verilog,综合工具为Xilinx XST。

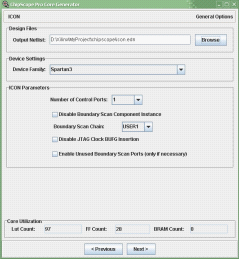

图6.62 ICON输出路径和FPGA系列设置对话框

图6.63 设置语言和综合工具

(6)生成ICON核。

如图6.64显示为生成的ICON核的相关信息,如发现有误,可以单击“Previous”按钮做修改后重新生成。

图6.64 生成ICON核

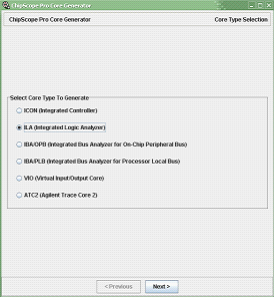

(7)选择集成逻辑分析仪(ILA核)。

生成ICON核后,单击“Start Over”按钮,回到核类型选择页,如图6.65所示,选择需要生成的核为ILA。

图6.65 生成集成逻辑分析仪

(8)设置输出路径、器件参数和时钟参数。

如图6.66所示为设置路径为新建工程所在路径,器件为Spartan3,采样时刻为时钟的上升沿。

图6.66 设置ILA输出路径、FPGA器件、采样时刻对话框

(9)设置触发参数。

触发参数的设置包括:触发端口数目(Number of input Trigger ports)、每个触发端口的触发宽度(Trigger Width)、触发条件判断单元个数(Match Units)和类型(Match Type)等。

此外,“Enable Trigger Sequencer”选项用于使能触发条件链。即设置触发条件为一“条件链”,只有依次满足“条件链”上的各个条件时才会被触发。如图6.67所示,如有与图中参数设置不一致之处,请自行修改。

(10)设置存储深度和数据位宽。

存储深度即在满足触发条件后要采集多少数据,存储深度的大小由FPGA的RAM资源大小决定。由于ChipScope所采集的数据都是保存在FPGA内部,因此存储深度的大小不能超过FPGA的RAM的最大值。如图6.68所示,选择“Data Same As Trigger”选项表示数据信号与触发信号相同,数据位宽即为触发端口的触发宽度。

(11)设置语言类型和综合工具。

如图6.69所示,本实例中选择Verilog及Xilinx XST。

fpga相关文章:fpga是什么

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论