基于NiosⅡ软核的嵌入式多路视频点播系统

引言

本文引用地址:https://www.eepw.com.cn/article/268262.htmVOD (视频点播)技术为人们提供了一种交互式的信息获取方式,并随着技术的完善不断扩展着其应用范围和影响力。

传统的VOD系统主要是以服务器作为视频的信息源,通过局域网进行点播,适合服务于住宅小区或公营机构。而对于缺乏网络支持、移动性较强的环境,如公共交通工具,传统的VOD系统显然难以实现。

本文针对特定的用户环境,提出采用Altera的SOPC(片上可编程系统)解决方案,利用NiosⅡ软核处理器和FPGA(现场可编程门阵列)配置灵活、 IP资源丰富、硬件设计和软件编程方便的特点,通过扩展IDE(集成开发环境)接口,以硬盘作为存储媒介,实现多路VOD系统的设计方案。该系统体积小、成本相对低廉,体现了嵌入式电子产品的优势。与传统的VOD系统相比,使用范围更具针对性,装配更灵活,升级扩展更方便,具有很广阔的前景。

1 系统功能划分

该系统从功能上可划分为系统控制核心、多路视频数据读取单元、视频解码模块和用户点播终端4个部分。

1.1 系统控制核心

系统以NiosⅡ软核为控制核心,主要负责硬盘初始化、提取视频节目簇链、生成节目列表、人机交互控制等工作。上电后,NiosⅡ控制器先初始化硬盘的传输模式和读写状态,然后读取主引导记录,寻址到基本分区的操作系统引导记录区,计算保留扇区和FAT(文件分配表)大小,分别得到FAT和根目录的入口。对目录树上的文件进行分析后,提取出视频文件的文件名、文件首簇,根据首簇指针再次查找FAT,追溯出文件的簇链,最后烧写到Flash存储器中。完成以上工作后,初始化中断,对用户端进行轮询,等待用户请求,分析用户指令包,作出相应响应。

1.2 多路视频数据读取

为实现海量视频数据的存取,该系统需外扩展硬盘作为存储介质。通过用户自定义的硬盘DMA(直接存储器存取)控制模块实现对硬盘数据的读写,功能包括为上层程序提供控制硬盘和多路数据输出的接口,产生硬盘DMA操作状态机信号。数据从硬盘读出后,以乒乓操作的方式交替存储在两片SRAM中,内存中的数据按照对应的输出端口并行排列。同时,根据用户终端提出的点播需求,数据往点播端口扇出。

1.3 视频解码

本系统采用外扩展的视频解码板作为硬解码模块。解码芯片是LSI LOGIC公司CL680视频CDMPEG 1音频/视频解码器。该芯片以CL480/484架构为基础,用于MPEG-1音频/视频解码,整合数字NTSC/PAL编码功能和加强KTV功能。

1.4 用户点播终端

为解决多用户终端远距离通信的问题,系统采用RS-485收发器作为主机与用户点播终端的连接桥梁。RS-485收发器采用平衡发送和差分接收,具有抑制共模干扰的能力,加上接收器的高灵敏度,能检测低达200 mV的电压,极大地提高信号传播的可靠性。

主机与终端间的通信方式采用类似令牌总线的通信协议。主机不断发出查询包,收到查询包的客户端被赋予发送控制命令的权限,客户端可选择发送命令或直接丢弃查询包,这样就避免了多个客户端同时向总线发送数据、导致通信失败的情况。

系统采用MB90092视频字符叠加模块,在用户终端屏幕中叠加功能菜单,建立友好的用户操作界面,用户可通过控制面板进行点播操作。

2 系统设计

2.1 系统硬件结构

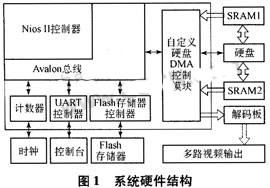

系统硬件结构如图1所示。

实现对硬盘的控制及两片内存的乒乓控制,系统使用了定制的DMA控制模块,通过SOPC Builder软件,以用户逻辑形式挂到Avalon总线上。

2.1.1 DMA控制模块

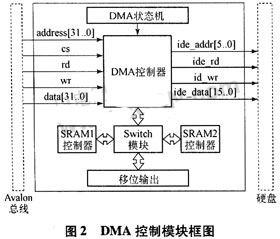

DMA控制模块框图如图2所示。

DMA 控制模块主要功能是控制硬盘进行多路视频数据的并发传输。为保证视频质量,需考虑到数据读写速度的提高。本系统采用按照ATA/ATAPI-6协议编写的 DMA模块,控制置硬盘以Ultra-DMA方式传输数据,可实现最大传输速率为66 Mbit/s,满足多路MPEG-1视频码流的并发传输。除了解决传输速率问题,该系统涉及到同时处理多路数据的读写,因此引入相应的功能子模块,以乒乓操作的方式控制两片SRAM的读写,并对多路数据的存储分区进行地址管理。

模块的主要子模块有DMA控制器、DMA状态机、switch和SRAM控制器。

DMA控制器作为Avalon总线与硬盘的接口,主要功能是接收上层程序的控制命令,再对硬盘的控制寄存器进行读写,在NiosⅡ程序的控制下将硬盘的传送模式设置为Ultra-DMA模式进行数据传输。

DMA 状态机模块是根据T13小组发布ATA(ATA/ATAPI-6)文档为设计标准,用Verilog HDL(硬件描述语言)实现的有限状态机。在控制终端的设置下传输方式转为Ultra-DMA模式后,硬盘向控制器发出DMA请求,此时DMA状态机启动。主机端向硬盘发送响应信号,握于成功,解除DMA STOP状态,同时使IDE_HDMARDY有效表示主控端已准备好。接着,数据流从硬盘流出,并发出一双沿锁存信号,SRAM控制器在该信号控制下将数据锁存入内存。直到DMA请求结束,STOP信号生效,DMA传输结束。整个过程遵守ATAPI-6协议,使用Verilog HDL描述出硬盘DMA传输过程的时序。

pid控制相关文章:pid控制原理

pid控制器相关文章:pid控制器原理

评论