射频模块解决调校和抗干扰难题

随着无线通信技术的进步,连网、数据和实时影音等无线传输的需求备受重视,而移动便捷和随时连网已成为使用者的生活之一。这一趋势不但促使产品的设计趋向“轻、薄、短、小”和多功能融合,具备高品质的无线连网功能更是成为了不可或缺的硬件开发关键。其中,微型化无线射频模块的设计正在符合如此广大的市场需求。

本文引用地址:https://www.eepw.com.cn/article/259914.htm由于一台移动设备需要开发的部分相当多,使用无线模块的分工方式将是加快开发时间的一种好方法——它可以有效简化系统的硬件设计,降低系统厂商的开发成本。又因为2.4GHz频段使用相当拥挤,无线射频模块对双频的需求也大幅提升。在接下来的文章中,将选用一款双频MIMO射频模块的设计应用做剖析,以提供给业界相关的工程人员参考。

模块IC与板上芯片(COB)的差别

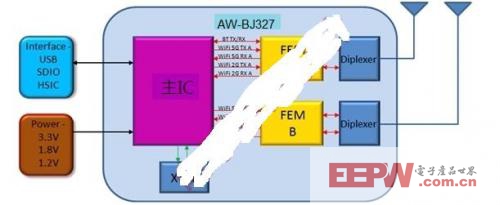

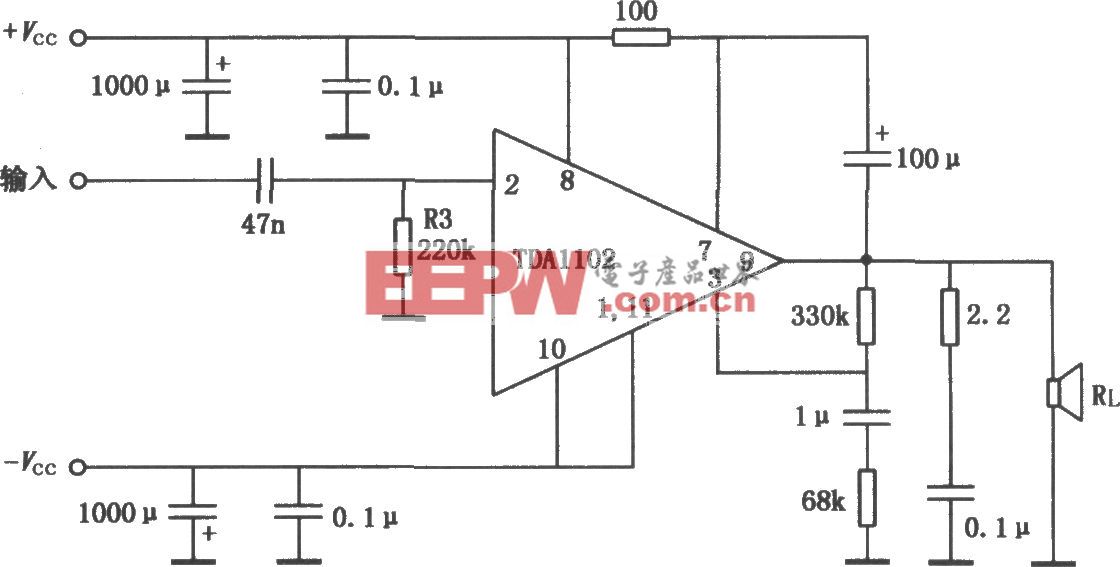

终端产品制造商往往会在选择模块IC还是COB时犹豫不决。采用COB的方式虽然乍看之下,在成本的考虑上似乎略胜过模块IC,然而,COB背后所需要的研发成本却有可能大过于使用模块IC。可以从目前最新的模块IC来做探讨。本文以AW-BJ327(参考型号)为例, 其芯片可同时支持2×2 MIMO 802.11a/b/g/n和蓝牙4.0功能。图1是AW-BJ327的系统框图。

图1:AW-BJ327系统框图。

AW-BJ327内部包含一颗主IC、一颗晶体振荡器、两颗前端模块(FEM)和两颗双工器,整体大小为15.1mm×10.2mm。外部的电路只需要几组电源滤波电容和两组匹配电路,便可使它工作。那么试想,如果要把这些电路用分立的方式在主版上实现,将会遇到哪些问题呢?首先,主IC部分采用的将会是球栅阵列(BGA)封装,而非模块IC使用的是芯片级封装(CSP)倒装芯片。一般而言,BGA将会比CSP的封装大上10~20%不等,因此将会降低空间的利用率。

一般,如果要将CSP的IC直接组装到主版上,则都会在CSP IC上点胶,以防止在跌落试验中造成IC脱落。而这会产生一个状况——如果IC发生问题了,将会遇到无法更换的窘境。

除组装技术外,就射频的技术层面来探讨,这也是一件困难且耗费时间的事情。5GHz的信号非常敏感并且容易受到干扰,更不用说采用的双工器是结合了2.4GHz和5GHz的2×2 MIMO。射频工程师将会花费大量时间来调校匹配电路和功率放大器。主IC需要对射频功能进行校准,校准的方面包含:发射机功率、I-Q、RSSI和晶振偏移量。在测试方面将会进行发射机功率、模板、EVM和接收机灵敏度的测试。以测试而言,如果要在终端产品上对它们进行全部测试,则将会极大地增加测试成本。每节省一秒测试时间就能够实现更大的产值。

模块IC则已经把功能上的调校和所有的测试项目都已经做完。终端厂商只需要管理电源以及外部的匹配电路就可以达到相同的效果。这极大地增加了便利性,尤其是降低了复杂度。终端系统商可以采用相对较少的人力和仪器,达到同样的效果。另外,由于电信系统商对于射频的规格要求越来越高(这也更增加了COB的难度),在这个与时间赛跑的开发时间里,采用模块IC的方式将会越来越普遍。

多重接口的弹性度

一般而言,低端的模块IC只提供了一到两个接口选择。手持式移动设备配备的接口通常会以安全数字输入输出(SDIO)接口为主,这使其在省电和传输速率上取得了平衡。具备省电优势的微型化无线模块对于移动设备而言非常重要,尤其是在省电模式和深睡眠模式下,都是以SDIO最为省电。AW-BJ327模块上也提供了省电模式和深睡眠模式相关的唤醒引脚或者掉电引脚,只要与系统CPU的GPIO引脚连接即可。这样,与SDIO接口同时使用时便能够实现更佳匹配。

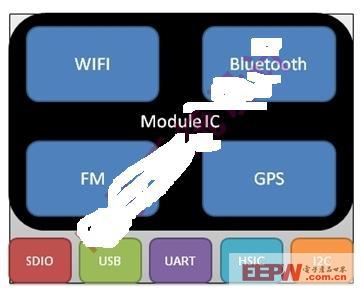

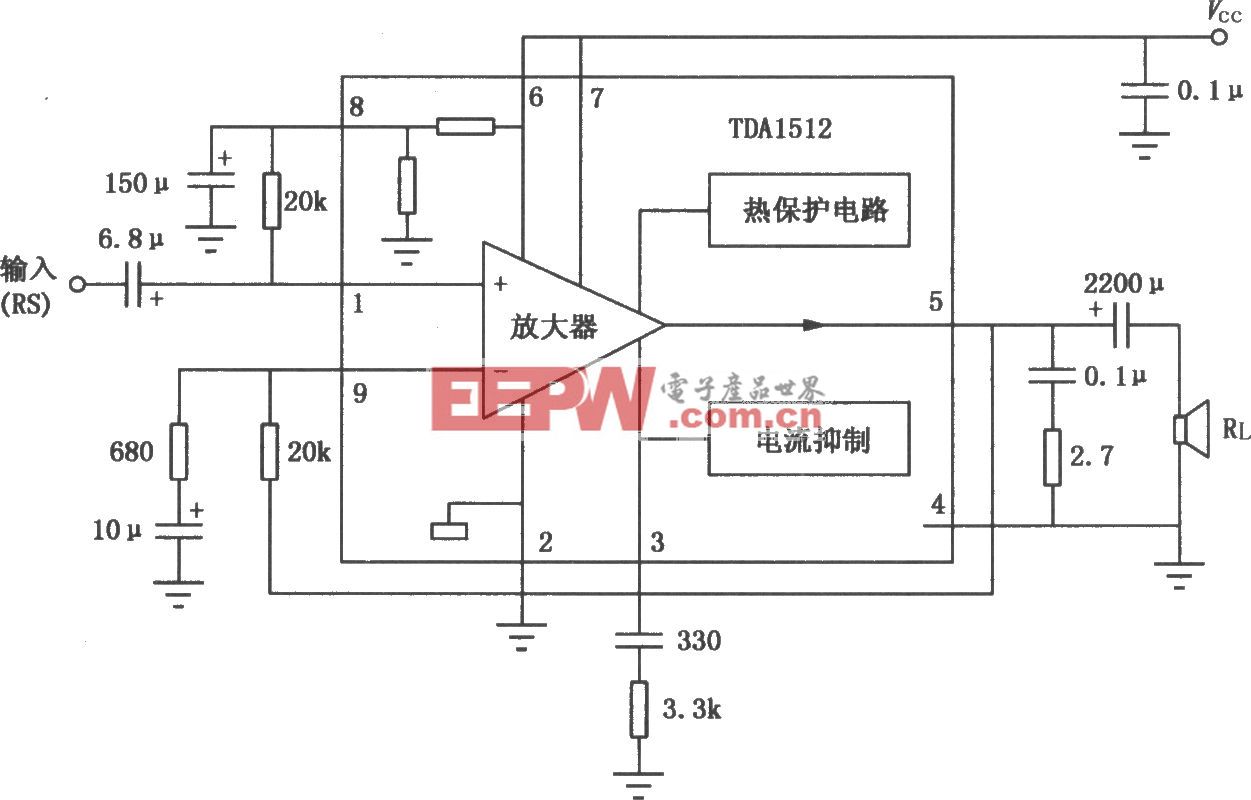

图2为一高端多任务模块IC与多重接口示意图,其模块IC将不只是提供单一接口或是提供一到两个接口以供使用,而是将所有常用的基本接口全部整合在一起。如此,便可以在单一模块上实现多重接口的选择,同时也可以增加客户使用设计上的弹性。

图2:高端多任务模块IC与多重接口示意图。

评论