数字射频存储器用GaAs超高速3bit相位体制ADC的设计与实现

1、引言

数字射频存储器(DRFM)具有对射频和微波信号的存储及再现能力,已发展成为现代电子战系统和仪器测试系统的重要组成部分。作为DRFM的核心部分,超高速ADC,DAC 的性能直接决定了它处理模拟信号的能力。但是,由于半导体工艺及器件性能的限制,高采样率、高分辨率的ADC 及DAC 难以实现。由于相位数字化比传统的幅度数字化有多种优点,且采用相位量化可降低对上述电路的要求,所以含相位体制ADC 及DAC 的DRFM 系统得到广泛应用。本文利用GaAs MESFET 全离子注入非自对准常规工艺设计了用于3bit 相位体制DRFM 系统的单片超高速相位体制ADC。测试结果表明,电路可在2GHz 时钟速率下完成采样、量化,达到1.2Gbp s 的输出码流速率,其瞬时带宽可达150MHz,具备±0.22LSB 的相位精度。

2、电路设计

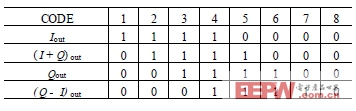

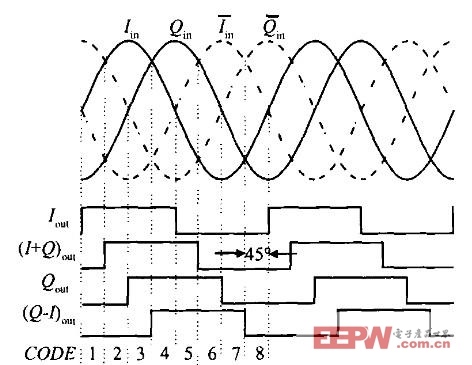

3bit 相位体制ADC的量化对象是输入信号的相位量,基本功能是将输入的两路正交模拟信号转换为四路含相位信息的数字信号。输出信号是占空比为1:1、频率与输入正交信号同频 率的方波信号,但每相邻两路之间的相位差为45°。3bit 相位体制ADC 的输入输出时序关系及真值表分别如图1、表1 所示。所以,3bit 相位体制ADC 的输出信号每周期含8 个相位态,电路的转换速率为输入模拟信号频率的8 倍。

表1、输出真值表

图1、输入输出时序图

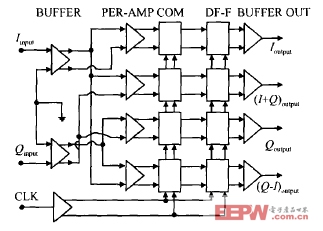

根据3bit 相位体制ADC 的工作原理,设计电路框图如图2 所示。

图2、3bit 相位体制ADC 电路框图

3bit 相位体制ADC 主要由五部分电路组成:(1)输入缓冲级。本级电路将输入的单端模拟正交信号变换为ADC 内部所需的互补信号,并具有一定的放大作用。此外,该级电路还包括将外部的单端时钟信号变换为内部其他各级电路所需的互补时钟信号。(2)预放大级。本级 电路根据3bit 相位量化的原理对模拟正交信号及其互补信号按照一定规则两两组合,进行差分放大。(3)比较级。本级电路在时钟作用下,利用正反馈原理对比较器输入端的模 拟信号进行取样、量化。(4)触发锁存级。本级电路在时钟的精确控制下,对前级比较级输出的量化数字值进行触发锁存。(5)输出缓冲级。目的是为了在高速 数字传输时能足以驱动ADC 后级的50Ω 负载。电路设计时,已将输入、输出端口设计为片内50Ω 匹配,便于高速测试及应用。

功分器相关文章:功分器原理

评论