基于ISA总线的ADSP21160链路口加载

引言

实时数字信号处理技术的核心及标志是数字信号处理器(DSP),DSP 现在广泛应用于雷达信号处理、各种通用信号处理、通讯、语音处理、图像处理及自动控制等各个方面。 随着实时数字信号处理技术的发展,单片DSP已无法满足诸如雷达信号处理等高速实时信号处理的发展要求。 AD公司的ADSP2106X,ADSP2116X系列浮点DSP采用超级哈佛结构、多级流水并拥有多达6个链路口,特别适合多片DSP级连,构成多处理器并行系统,因此广泛应用于雷达等高速实时信号处理系统。

当ADSP用户产生用户代码,并进行了软件及硬件仿真后,接下来要做的就是将程序代码加载到DSP内部程序空间,使程序代码脱离仿真环境,直接运行在硬件板卡上。本文主要介绍ADSP21160的三种主要加载方式之一-链路口加载,并附带介绍了ADSP21160的链路口及通用计算机的ISA总线。

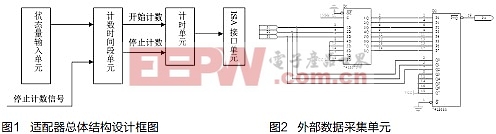

图 1 ISA与Link port的接口电路

ADSP21160链路口的特点和功能

?各链路口可以独立、同时工作;

?链路口数据可以打包成32位、48位,被处理器核访问,与片内存储器作DMA传输;

?外部主机可以直接访问链路口;

?双缓冲的发送和接收寄存器;

?通过时钟/确认信号在链路通信时握手,每个链路均可收/发数据,并分别由一个DMA通道支持;

?利用链路连接可以组成一维到多维的多种形式的处理器网络。

链路口的信号握手

链路口握手信号包括LxACK和LxCLK,可在ADSP21160之间进行异步数据传输,其它遵守同样协议的外部设备也可与链路口进行通信,本文介绍链路口通过可编程器件CPLD与与ISA总线通信。链路口以8位码一组的方式发送32位或48位字,发送方在LxCLK的上升沿送出8位码,接收方利用时钟下降沿锁存8位码,接收方使LxACK有效,表示已准备接收下一个字。在每个字发送开始时,发送方如果看到LxACK无效,将使LxCLK为高,并等待LxACK有效后才开始发送新字。接收缓冲器为满时,接收方将使LxACK无效。当发送缓冲器为空时,LxCLK将保持为低。当作为发送方时,链路口驱动LxCLK和LxDAT7~0;当作为接收方时,链路口驱动LxACK以进行数据发送及握手。

ADSP21160的引导模式

在加电复位后,ADSP21160可以自动从外部设备加载程序,称为引导。ADSP21160支持3种引导模式:prom、host、link port。另外还可以选择no boot模式及通过JTAG口加载程序。常用的引导模式有prom 引导和link port引导。

对于prom 引导,DSP的BMS作为输出接EPROM片选信号线,EPROM的8位数据线接ADSP21160的DATA32~DATA39,对于多处理器共享系统,可以用一片EPROM对所有的ADSP21160加载,即把所有处理器的BMS接在一起,只有主处理器的BMS被驱动。

对于link port 引导,DMAC6控制寄存器为A0H,链路缓冲4(LBUF4)指定到链路口4,用于加载外部程序,数据以8位形式在LxCLK上升沿由其它ADSP21160的link port或外部设备发送,在LxCLK下降沿锁存到接收DSP的LBUF4中。加载程序的外部设备可以直接向链路口缓冲写入数据,只要写入速率不超过DSP的主时钟频率即可。而此处的外部设备采用计算机的ISA总线,采用CPLD进行link port 与ISA的接口设计,使ISA的输出满足link port 的协议。通过地址译码将ADSP21160的link port映射为一个I/O端口,采用I/O端口写操作,将数据从计算机发送到ADSP21160的link port,以实现DSP的链路口加载。

加载程序采用C++语言编制,首先通过译码端口向链路口缓冲写256X48位的引导码,间隔大约50ms后加载剩余程序代码。两段程序发送有一段时间间隔是由于发送完引导码后,引导码在DSP内部执行,进行初始化,初始化完毕后才可加载剩余的程序代码,否则将导致加载失败。另外,要注意向链路口缓冲写数据不能太快,否则将有数据丢失,导致加载失败。

ISA总线及其与link port的接口

ISA总线主要用于计算机对接口板的控制及相互之间的数据传输。由于link port只有8根数据线,所以,对于ISA,采用其基本的62根线,而不需要36根扩展插槽。本接口电路只使用地址线A0~A9,数据线D0~D7,及控制线AEN,WR,I/OCHRDY。其中地址线A0~A9实现地址译码;数据线D0~D7进行数据传输;控制线AEN参与译码以区分总线的CPU控制和DMA控制器控制,当AEN 为低电平时,由CPU控制总线,当AEN为高时,由DMA控制器控制总线; WR信号驱动I/O端口写,将数据从计算机发送到ADSP21160 的链路口;I/OCHRDY用于计算机与ADSP21160的link port的握手。为了将数据从计算机发送到link port ,需将ADSP21160的link port 4译码成一个I/O端口。计算机有1024个I/O端口,其中留给外部设备的的端口为0X100~0X3FF,这其中大多数又为各种计算机常用外设所占用 ,实际用户可用的地址为0X300~0X31F,本接口电路采用0X300作为ADSP21160的link port 的口地址。

ISA与link port的接口电路由Altera公司的可编程器件CPLD实现。考虑到此接口电路的复杂程度,采用MAX7000S系列的EPM7064S 来实现。用CPLD实现接口电路具有以下特点:

?高性能;

?高集成度:多种组合及时序电路可在一片CPLD上完成;

?开发周期短:通过软件编程即可完成各种组合电路及逻辑电路的设计,过去需要几天才可完成的任务,现在几个小时甚至几十分钟即可完成;

?可在线修改:通过下载线可方便的将 pof文件传输到CPLD而无需将其从板上取下来,极大的方便了设计;

?CPLD的输入及输出管脚可自由安排,有利于实现良好的PCB布线,特别适用于PCB 板上器件较多的情况。

ISA与link port 的接口电路

接口电路如图1所示。由A0~A9及WR、AEN作为CPLD的输入,CPLD实现译码及驱动,将link port 的I/O端口地址译码为0X300,CPLD的输出CPLDLxCLK接到link port的LxCLK,CPLDLxCLK与ISA的WR反相;计算机ISA总线的D0~D7经CPLD缓冲隔离,接到link port的DATA0~DATA7;link port 的LxACK通过OC门接到ISA的I/OCHRDY。当计算机发出I/O写时,在写信号的下降沿时,计算机将数据发送到数据线,此时CPLDLxCLK为上升沿;在写信号的上升沿,即CPLDLxCLK的下降沿,link port 将数据线上的数据锁存。如果link port的LBUF 为满,则将其LxACK驱动为低,ISA的I/OCHRDY接收到此信号后将使WR保持低电平,CPLDLxCLK保持高电平,数据一直保持在数据线上。直到link port 的LBUF不满时,link port 驱动其LxACK为高,ISA的I/OCHRDY接收到此信号后将使WR由低变高,即CPLDLxCLK由高变低,在CPLDLxCLK下降沿数据线上的数据被link port锁存到其数据缓冲器LBUF 。若无写信号,则ISA的WR信号为高电平,此时CPLDLxCLK为低电平,则link port的LxCLK信号亦为低电平,link port 不会接收任何数据。

结语

以上接口电路运用于某雷达信号处理平台的程序加载,运行良好。最初接口电路的验证是通过使用该接口电路加载简单测试程序完成的。因为该信号处理板上ADSP21160的FLAG1引脚外接LED(发光二极管),当FLAG1置高,LED亮。测试程序的主要功能是置FLAG1为高。加载程序运行大约2秒后,LED亮,表示加载成功。■

参考文献

1 苏涛,吴顺君.高性能DSP与高速实时信号处理(第二版)

2 ADSP-21160 SHARC DSP Hardware Reference.1998

3 赵曙光,郭万有.可编程逻辑器件原理、开发与应用

4 李伯成,候伯亨.微型机应用系统设计

评论